SISO, SIPO, PISO, PIPO: Shift Register Modes

TL;DR: A shift register is a chain of flip-flops with a shared clock. Pick where the data enters and exits — serially or in parallel — and you get four modes: SISO (delay line), SIPO (serial-to-parallel converter, used in UART receivers), PISO (parallel-to-serial converter, used in UART transmitters), and PIPO (parallel-load broadside register). The 74194 universal shift register supports all four with a 2-bit mode select.

A shift register is a row of D flip-flops wired in series, sharing a single clock. On every clock edge, each flip-flop captures the value of the one to its left, and bits march through the register one position at a time. That is the whole mechanism. What changes from one shift register to the next is where you connect the inputs and outputs — and those four choices give the four standard operating modes.

The Four Modes at a Glance

Each mode is named by combining input and output styles:

| Mode | Input | Output | Typical use |

|---|---|---|---|

| SISO | Serial | Serial | Delay line, bit-stream pipeline |

| SIPO | Serial | Parallel | UART receiver, serial-to-parallel deserialiser |

| PISO | Parallel | Serial | UART transmitter, parallel-to-serial serialiser |

| PIPO | Parallel | Parallel | Broadside register, parallel-load latch |

The same flip-flop chain underlies all four. The difference is which signals you expose and how the data enters or exits the chain.

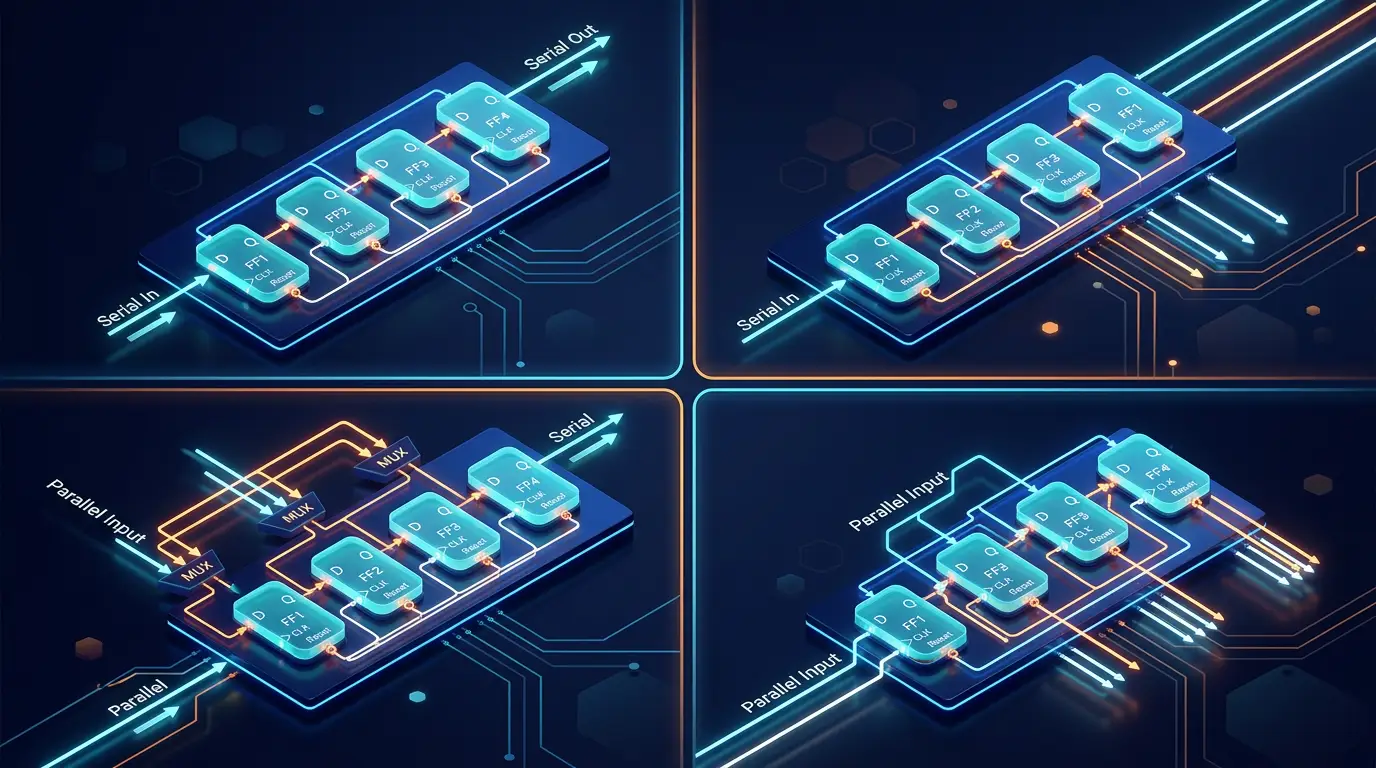

SISO: Serial-In, Serial-Out

The simplest form. One serial input on the leftmost flip-flop, one serial output on the rightmost. Bits enter on each clock and emerge clocks later, where is the number of stages.

SI ──[FF0]──[FF1]──[FF2]──[FF3]── SO

^ ^ ^ ^

| | | |

+------+------+------+

CLKA 4-bit SISO register delays a serial bit stream by 4 clock cycles. Feed in 1 0 1 1 0 1 0 0 and the same pattern emerges 4 cycles later on SO.

Use cases.

- Bit-stream delay. Synchronisation of two streams that need to match at a specific clock offset.

- Pipeline registering. Inserting a programmable number of clocks between two parts of a longer pipeline.

- Echo/delay effects. The same idea in audio DSP, where the “shift register” is a memory-based circular buffer.

A SISO register is the smallest useful shift register and the only mode that does not require any per-stage I/O. The 4-bit shift register SISO template is the cleanest place to see the shift behaviour without any of the other modes’ complications.

SIPO: Serial-In, Parallel-Out

SIPO accepts a single serial input but exposes the output of every flip-flop in parallel.

Q3 Q2 Q1 Q0

| | | |

v v v v

SI ──[FF0]──[FF1]──[FF2]──[FF3]

^ ^ ^ ^

+------+------+------+

CLKAfter clock cycles, the parallel outputs hold the most recent serial bits, with the oldest bit at one end and the newest at the other (the order depends on whether bits enter the left or right end of the chain).

Use cases.

- UART / RS-232 receiver. A UART reads a serial bit stream one bit per bit-clock. Eight clocks later, all 8 data bits are visible in parallel and can be moved to the rest of the system.

- Display drivers. A daisy-chained string of 74HC595 SIPO shift registers drives an LED matrix from a 3-pin SPI-style connection. See the shift register guide for an extended walk-through of this pattern.

- Sensor protocols. SPI ADCs, temperature sensors, and similar parts clock their output bits out serially; the host SIPO-shifts them into a register for parallel use.

Worked Example: Loading 1011 into a 4-Bit SIPO

Start with all flip-flops at 0. Drive SI with the bit pattern 1, 0, 1, 1 over four clock cycles. Bits enter at and shift toward — the convention used by most TTL-family parts.

| Clock | SI | ||||

|---|---|---|---|---|---|

| Initial | — | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 0 | 1 | 0 |

| 3 | 1 | 0 | 1 | 0 | 1 |

| 4 | 1 | 1 | 0 | 1 | 1 |

After four clocks, the parallel output is Q3 Q2 Q1 Q0 = 1011 — exactly the serial pattern that was fed in, now visible in parallel. The register has just performed a serial-to-parallel conversion.

Notice the bit order. The first bit in (1) ends up in — the leftmost output — because it has been shifted three positions during the four clocks. Whether that “first bit” is interpreted as the MSB or the LSB of a byte is a protocol choice, not a property of the shift register itself: SPI defaults to MSB-first; UART/RS-232 sends LSB first. The hardware is identical in either case — only the receiver’s bit-mapping logic decides which corresponds to bit 7 versus bit 0. The 8-bit SIPO shift register template lets you toggle the bit order and watch the parallel pattern reassemble.

PISO: Parallel-In, Serial-Out

PISO is the inverse. Each flip-flop has a parallel data input plus the usual shift input, and a mode-select line picks between load and shift.

P0 P1 P2 P3

| | | |

v v v v

[FF0]──[FF1]──[FF2]──[FF3]── SO

^ ^ ^ ^

+------+------+------+

SHIFT/LOAD

CLKWhen SHIFT/LOAD is asserted to load, the next clock edge captures in parallel. When SHIFT/LOAD is asserted to shift, subsequent clocks shift the loaded value out one bit at a time on SO.

A PISO is implemented per-stage by feeding the D input of each flip-flop through a multiplexer: mode 0 picks the parallel input, mode 1 picks the previous flip-flop’s output. One mode-select line wires to all the muxes; one clock wires to all the flip-flops.

Use cases.

- UART / RS-232 transmitter. The CPU writes a parallel byte to the UART transmit register; the UART loads it into a PISO and shifts it out at the bit-clock rate.

- SPI master. SPI sends 8, 16, or 32 bits at a time, and the master almost always implements transmission as a PISO load-and-shift.

- Fast parallel-to-serial conversion. Any place a wide internal bus has to be sent over a serial wire.

The 8-bit serial transmitter/receiver template wires a PISO transmitter to a SIPO receiver across a single shared clock — a minimum-viable serial link.

PIPO: Parallel-In, Parallel-Out

The fourth mode treats the shift register as a plain -bit register: parallel inputs, parallel outputs, no shifting at all.

P0 P1 P2 P3

| | | |

v v v v

[FF0][FF1][FF2][FF3]

| | | |

v v v v

Q0 Q1 Q2 Q3A PIPO is just a 4-bit register with a load enable. Every flip-flop captures its parallel input on the active clock edge; outputs update simultaneously. The mode is included in the shift-register taxonomy because most universal shift-register parts can operate this way as one of their selectable modes.

Use cases.

- Pipeline stages. A row of D flip-flops between two combinational blocks is a PIPO.

- CPU general-purpose registers. Same primitive, more of them — the REGISTER component reference describes the same building block.

- Synchronisation barriers. Capture all of a wide bus on a single edge, regardless of the per-bit propagation delay through prior logic.

PIPO is the mode you almost certainly already use without thinking of it as a shift register; the broadside register is everywhere in synchronous design.

Bidirectional and Universal Shift Registers

Real parts often combine multiple modes behind a small mode-select code.

Bidirectional shift register. Adds a “shift right vs shift left” choice. Each flip-flop’s D input is selected by a mux: the right-neighbour’s Q for shift-left, the left-neighbour’s Q for shift-right.

Universal shift register. Combines bidirectional shifting with parallel load and hold. The classic part is the 74194, a 4-bit synchronous universal shift register with a 2-bit mode-select code:

| Mode | ||

|---|---|---|

| 0 | 0 | Hold (no change on clock) |

| 0 | 1 | Shift right |

| 1 | 0 | Shift left |

| 1 | 1 | Parallel load |

Internally, each stage is a 4-to-1 mux feeding a D flip-flop. The mux selects, in order: the same flip-flop’s current Q (hold), the right-neighbour’s Q (shift right), the left-neighbour’s Q (shift left), or the parallel input. One 74194 — or any of its functional equivalents in modern HDL libraries — covers all four base modes plus left/right reversal.

The SHIFT_REGISTER component in the simulator is a parameterised version of this idea, and the basic REGISTER is its no-shift, parallel-load-only sibling.

Mode Selection: When to Use Which

The choice is dictated almost entirely by the I/O the rest of the system presents.

| Situation | Mode | Why |

|---|---|---|

| Bit-stream delay or pipeline gap | SISO | Only need one wire each side; chain length is the delay |

| Serial input to be read in parallel | SIPO | Capture serial protocol bytes for parallel processing |

| Parallel value to be sent serially | PISO | Send bytes over a serial pin without losing a clock |

| Wide bus needs an edge-aligned snapshot | PIPO | Same edge captures all bits simultaneously |

| Need to support multiple modes at runtime | Universal (74194-style) | Mode-select code picks behaviour per cycle |

For new designs in HDL, the distinction often disappears in source code: a synthesised always block describes the data flow and the synthesiser maps it onto the appropriate flip-flop and mux topology. But in discrete logic and when reading datasheets, the four-letter taxonomy remains the standard vocabulary.

Common Pitfalls

A few details bite people the first time.

Bit order matters. Same hardware can produce LSB-first or MSB-first output depending on which end of the chain you call . UART is LSB-first; SPI defaults to MSB-first. A wrong choice produces a perfectly mirrored result that is not obviously broken.

Single-clock domain. All flip-flops in a shift register must share the same clock. Bringing in data from a different clock domain requires a synchroniser, not just a SIPO — see the setup/hold and metastability post for the failure mode you avoid by doing this correctly.

Reset and initial state. A shift register without a reset comes up holding the random power-on values of its flip-flops. SIPO receivers in particular need a synchronous or asynchronous reset so the parallel output is meaningful before any bits have arrived.

Mode transitions. On a 74194, switching from “shift” to “load” must be done with the mode-select stable at the active clock edge. A glitch on the mode line near the edge can land in the parallel-load mux and corrupt the register. The basic clock pulse discussion has more on edge timing for shared-clock designs.

Build It in the Simulator

Three small experiments cover all four modes.

-

SISO delay line. Open the 4-bit shift register SISO template and feed a square wave to SI. Confirm the output is the same square wave delayed by 4 clock cycles.

-

SIPO conversion. Open the 8-bit SIPO shift register template, drive SI with a known byte one bit per clock, and watch the parallel outputs fill from to . Add OUTPUT_LIGHTs to make the byte legible.

-

PISO transmission. Use the 8-bit serial transmitter/receiver template to load a parallel byte, then assert shift mode and watch the byte clock out one bit per cycle on the SO line. The companion SIPO at the receive end reassembles it.

For a fourth, build a PIPO: drop a REGISTER component and wire its inputs and outputs in parallel. The same primitive, used differently.

What’s Next

Shift registers are the substrate for all of serial communication. The next post in the series, parity-bit tutorial — single-bit error detection, shows how a serial protocol layers a one-bit error check on top of a SIPO/PISO pair to detect transmission errors. The Hamming-code post that follows extends parity to actual error correction, again using shift registers as the underlying transport.

Open the basic shift register demo template for a stripped-down version that exposes the inner state, then graduate to the universal-mode template once the four base behaviours feel routine.