Clock Skew and Its Effect on Timing

TL;DR: Clock skew is the difference between when a clock edge arrives at one flip-flop and when it arrives at the next. Positive skew (the receive flip-flop sees the edge later) relaxes setup margin but eats hold margin; negative skew does the opposite. Real chips manage skew with balanced clock distribution networks — H-trees or grids built by clock-tree synthesis — and sometimes inject useful skew on purpose to extend a critical path.

A synchronous digital system is built on a comforting fiction: every flip-flop sees the same clock edge at the same instant. In a real chip the clock has to travel through wires and buffers that have non-zero delay, and no two paths are exactly equal. The arrival-time difference between two flip-flops is clock skew, and once you account for it the timing equations look noticeably different from the zero-skew classroom version.

What Clock Skew Is

Define as the clock period and call two flip-flops the launch and capture registers. The launch flip-flop opens its output on a clock edge, the combinational network between them propagates the new value, and the capture flip-flop samples that value on the next clock edge.

Clock skew is the arrival-time difference of the same clock edge at the capture flip-flop versus the launch flip-flop:

Positive skew means the capture clock arrives later than the launch clock. Negative skew means the capture clock arrives earlier. Pure zero skew is a useful textbook idealisation; in real silicon it is achieved approximately, never exactly.

The launch flip-flop also has its own internal clock-to-Q delay , and the capture flip-flop has its own setup time and hold time . Together with combinational delay these produce the timing equations that determine whether the design works. The basics live in the propagation delay post and the setup/hold metastability post; this article focuses on what skew adds.

How Skew Changes the Setup Equation

The classical setup-time inequality says the data must arrive at the capture flip-flop before the next clock edge, with to spare:

Now include skew. The capture clock arrives later than the launch clock, so the data has time to propagate before the capture edge:

Positive skew helps setup. The data is given extra time before the capture edge fires. Equivalently, you can run the clock faster:

Negative skew hurts setup. The capture edge arrives earlier than expected, and the data has less time to make it through.

How Skew Changes the Hold Equation

Hold-time analysis worries about the opposite problem: the data after the launch edge must not arrive at the capture flip-flop too quickly, or it would corrupt the value being sampled at this same clock edge. The zero-skew form is:

With skew, the capture edge happens later, so the new data has extra time to race through and clobber the current sample:

Positive skew hurts hold. The same condition that helps setup makes hold harder to satisfy. Negative skew, conversely, helps hold and hurts setup.

This is the central tension of skew analysis. Setup violations limit the maximum frequency of a chip; hold violations are even worse because they cannot be fixed by slowing the clock down — slowing the clock does not change either the launch-to-capture data race or the skew. A hold violation means the chip is broken at any speed and only buffer insertion or layout repair will fix it.

Maximum Clock Frequency with Skew

Combining setup and the launch flip-flop’s own clock-to-Q gives the maximum operating frequency:

Concretely, suppose:

- (positive)

Then , or . Without the skew the same path would max out at , or . The 0.5 ns of useful skew bought 28 MHz of headroom — but only on this single path, and only if every other path along the same launch-capture pair also has positive hold margin.

Negative skew of the same magnitude would give , dropping to 200 MHz.

Where Skew Comes From

Skew is always the integrated effect of many small differences along the clock distribution network.

Wire length. A clock signal that travels 5 mm to flip-flop A and 3 mm to flip-flop B sees roughly 6 ps/mm of RC delay difference (process-dependent). Multiply by a few millimetres of wire mismatch and you have hundreds of picoseconds of skew, which is significant at GHz clocks.

Capacitive load. Each flip-flop and clock buffer presents some load to the clock signal. A clock buffer driving 8 flip-flops has roughly twice the load of one driving 4, so its output transitions more slowly and its downstream edges arrive later.

Buffer chain depth. Modern ASICs use trees of clock buffers to drive thousands of flip-flops without a single buffer being asked to drive too much load. If two flip-flops are at the bottom of buffer chains of different depth, they see different cumulative buffer delay and therefore different clock arrival times.

Process variation. Two physically identical buffers in different parts of the same die can have different effective delays because of dopant variation, threshold-voltage mismatch, or oxide thickness drift. This is the on-chip variation (OCV) component of skew.

Voltage and temperature gradients. A buffer in a hot region of the die switches more slowly than one in a cold region. Voltage IR drop produces the same effect — a buffer near a power-grid weak spot sees a lower local supply and runs slower.

The BUFFER component reference describes the standard cell that clock-tree synthesis tools insert to balance these effects. Buffer placement is the primary lever the tool has to drive skew toward zero.

Clock-Tree Synthesis and Distribution Topologies

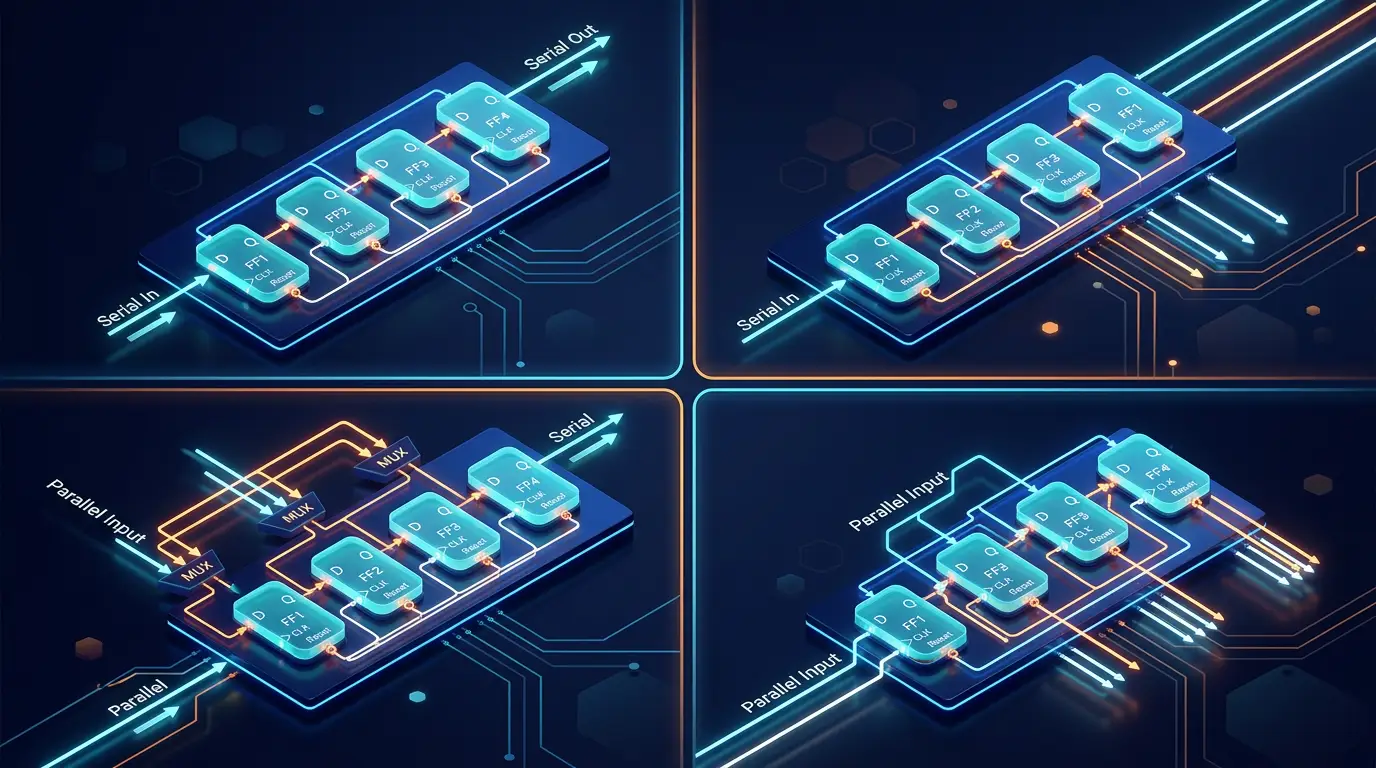

The job of distributing a clock from a single source to thousands or millions of flip-flops with minimal skew is clock-tree synthesis (CTS). The tool builds a balanced tree of buffers such that every leaf (every flip-flop’s clock input) sees roughly the same number of buffers and roughly the same wire length back to the root. There are several common topologies.

H-tree. A symmetric recursive H-shape. The clock arrives at the centre of an H; each end of the H launches a smaller H rotated 90 degrees; recursion bottoms out at individual flip-flops. By construction every leaf is the same distance from the root, so wire-length skew is zero in the ideal case. Used in microprocessor cores and memory arrays where the layout is regular enough to support the symmetry.

Balanced buffer tree. A general fan-out tree where every path from root to leaf has the same number of buffers and roughly equal wire length. Less constrained than an H-tree, used in random-logic blocks where flip-flop placement is not regular. CTS tools build these automatically.

Clock mesh / grid. A two-dimensional mesh of clock wires fed from many drivers in parallel. Every flip-flop taps the nearest mesh intersection. Mesh distribution averages out local skew at the cost of significant power — the mesh is always switching at the clock frequency. Used in high-performance CPUs (e.g., Intel and IBM POWER) where skew has to be sub-50 ps across centimetres of die.

Skew-aware placement. The tool places flip-flops with timing in mind, not just area, so that critical-path launch-capture pairs end up in the same clock region.

The output of CTS is reported as a skew budget: the maximum measured arrival-time difference between any two flip-flops that share a clock domain. A typical budget for a modern ASIC at GHz frequencies is 50–100 ps; a modest FPGA design might tolerate 200–500 ps.

Useful Skew

Sometimes you want skew. If a critical path is too slow to meet timing at the desired frequency, you can introduce useful skew by intentionally delaying the capture flip-flop’s clock relative to the launch flip-flop’s clock. The data path gains of extra time to settle.

The price is paid downstream. The capture flip-flop is now the launch flip-flop for the next path, and that next path now has less time. Useful skew is a redistribution, not a creation. The technique works when the path you are stealing from has slack to spare and the path you are giving to is the critical one.

Modern CTS tools support useful-skew insertion as an optimisation pass: identify the critical path, compute how much skew can be borrowed without breaking neighbouring paths, and insert the buffers that produce it. The same lever is used in some D flip-flop-heavy pipelines where one stage is consistently slower than the others; rather than rebuilding the whole pipeline, the tool buys it the time from its neighbours.

The same flip-flop primitive that lives in every 4-bit register — and the same D flip-flop explainer — is the consumer of a CTS clock tree. From the flip-flop’s perspective, the clock is just the clock pulse that arrives some number of picoseconds after the launch’s clock arrived.

Skew vs Jitter

The two are often confused. Both are forms of clock-edge uncertainty, but they live on different time scales.

Skew is the spatial difference between two flip-flops on the same clock cycle. It is fixed by routing and process; it does not change from cycle to cycle (except slowly, with temperature and voltage drift).

Jitter is the temporal variability of a single flip-flop’s clock edge from one cycle to the next. The same flip-flop sees the rising edge at on cycle 1, on cycle 2, and on cycle 3. Jitter comes from PLL noise, supply ripple, thermal noise in clock buffers, and sometimes signal-integrity coupling from neighbouring wires.

| Property | Skew | Jitter |

|---|---|---|

| Domain | spatial (between flip-flops) | temporal (cycle to cycle) |

| Source | wire delay, buffer delay, OCV | PLL noise, supply noise, thermal |

| Mitigation | clock-tree synthesis | PLL design, supply decoupling |

| Cycle-to-cycle | constant per pair | varies every cycle |

For a setup-time budget you typically subtract both: , where jitter is added because it can fall in either direction and must be assumed to fall the wrong way. In practice timing tools track jitter as a separate budget item and propagate it through every path.

Skew in a Simulator vs Skew in Silicon

A digital simulator running an idealised model gives every flip-flop the same clock edge instant — zero skew by construction. That is fine for verifying functional correctness, and it is what most teaching simulators including DigiSim do by default. The skew effects discussed here only show up when you start modelling per-net delays or simulating at the gate level with realistic timing back-annotation.

Two practical exercises that can be done in a functional simulator:

- Build a long shift register that runs at the highest clock rate the simulator allows, and add a deliberate delay buffer in the clock path of one stage. The downstream stages will lose data when the skew exceeds the launch-to-capture data delay.

- Compare two pipelines, one with the 4-bit register all sharing a single clock and one with each register clocked from its own CLOCK source. The second design is functionally identical only when the two clocks happen to agree; introduce a phase offset and the data starts shifting at the wrong moment.

These don’t measure skew in the picosecond sense, but they teach the right intuition: a clock is not a free signal, and the times-of-arrival matter as much as the values.

What’s Next

Clock skew on the sequential side has a combinational sibling: races between paths of unequal delay can produce static and dynamic glitches even before any flip-flop gets involved. The upcoming static vs dynamic hazards in combinational logic post walks through the same delay-mismatch story for AND-OR networks and shows how a redundant K-map cover term eliminates the glitch entirely.

Open the d-flip-flop with controls template to experiment with clock-input timing on a single flip-flop, then try adding a buffer chain to the clock to see how the effective sample point moves.