Mealy vs Moore State Machines: With Examples

TL;DR: A Mealy machine’s outputs depend on both the current state and the current inputs; a Moore machine’s outputs depend only on the current state. Mealy machines tend to use fewer states and react faster, but their outputs can glitch when inputs change asynchronously. Moore machines need more states but produce clean, glitch-free outputs that are valid for the entire clock cycle. Most safety-critical and bus-facing designs use Moore; most compact protocol decoders use Mealy.

Every clocked digital system that “remembers” what it has been doing is, in the formal sense, a finite state machine. A clock-divider counter is one. A USB packet decoder is one. The control unit of every CPU you have ever used is one. The two canonical styles for building these machines — Mealy and Moore — differ on a single design decision: should the output depend on the inputs, or only on the state? That single choice cascades into measurable differences in state count, output stability, propagation delay, and the kind of bugs you will hunt down at 2 a.m.

This post walks through both styles using two concrete worked examples — a traffic light controller and a “1011” sequence detector — and compares them on every dimension that actually matters. You will come away with a usable mental model for picking the right style, an encoding strategy (binary vs one-hot), and a clear sense of where each pattern shines.

What Is a Finite State Machine, Really?

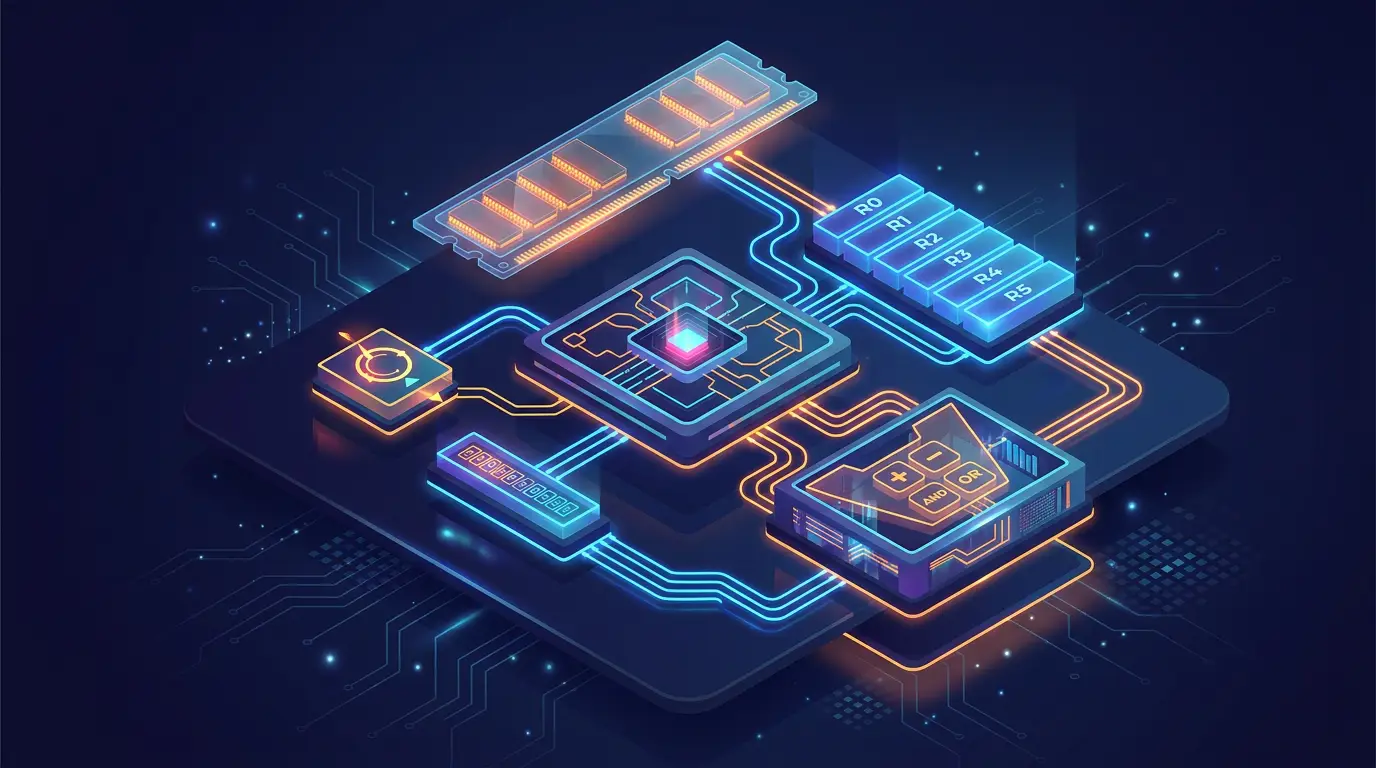

A finite state machine is a circuit with three pieces:

- A state register. A bank of D flip-flops that holds the current state. The number of flip-flops sets the maximum number of distinguishable states ( states for flip-flops in binary encoding).

- Next-state logic. A combinational block that consumes the current state plus any inputs and produces the next state — the value the state register will load on the next clock edge.

- Output logic. A combinational block that produces the FSM’s outputs. This block is where Mealy and Moore differ.

In a Mealy machine, the output logic takes both the current state and the current inputs:

In a Moore machine, the output logic only takes the current state:

The next-state logic is identical in both styles — only where the output wires are tapped from differs. That single difference is responsible for everything that follows.

If you have not built a state-holding circuit before, the right warm-up is Counters and State Machines: Controlling Digital Sequences. The state register itself is a standard REGISTER component.

Mealy Machines: Output Depends on State and Input

Picture a Mealy machine as a graph where each transition arrow is labeled input/output. The output appears during the transition, the moment the input arrives — combinational with respect to the input.

in=0/out=0

┌─────────────┐

│ │

▼ │

S0 ──────────► S1

in=1/out=1

│

│ in=0/out=0

└──────► S0Properties:

- Fewer states — outputs can be encoded in transitions, so the same logical state can be reused for multiple output cases.

- Faster reaction — the output changes the same cycle the input changes (potentially within the cycle, asynchronously, depending on input timing).

- Output is unstable — if the input glitches mid-cycle, the output glitches with it. The output is only valid at the clock edge, not for the entire cycle.

Moore Machines: Output Depends Only on State

In a Moore machine the output is a label on the node — the state itself — not the edges. Outputs change only at clock edges, so they are guaranteed stable for an entire cycle.

in=1

┌─────────────┐

│ ▼

S0(out=0) S1(out=1)

▲ │

└─────────────┘

in=0Properties:

- More states — every distinct output requires a distinct state.

- Slower reaction — the response to an input only appears one clock cycle later, after the state register has captured the new state.

- Output is glitch-free — outputs are valid for the full clock period, sandwiched between two clean edges.

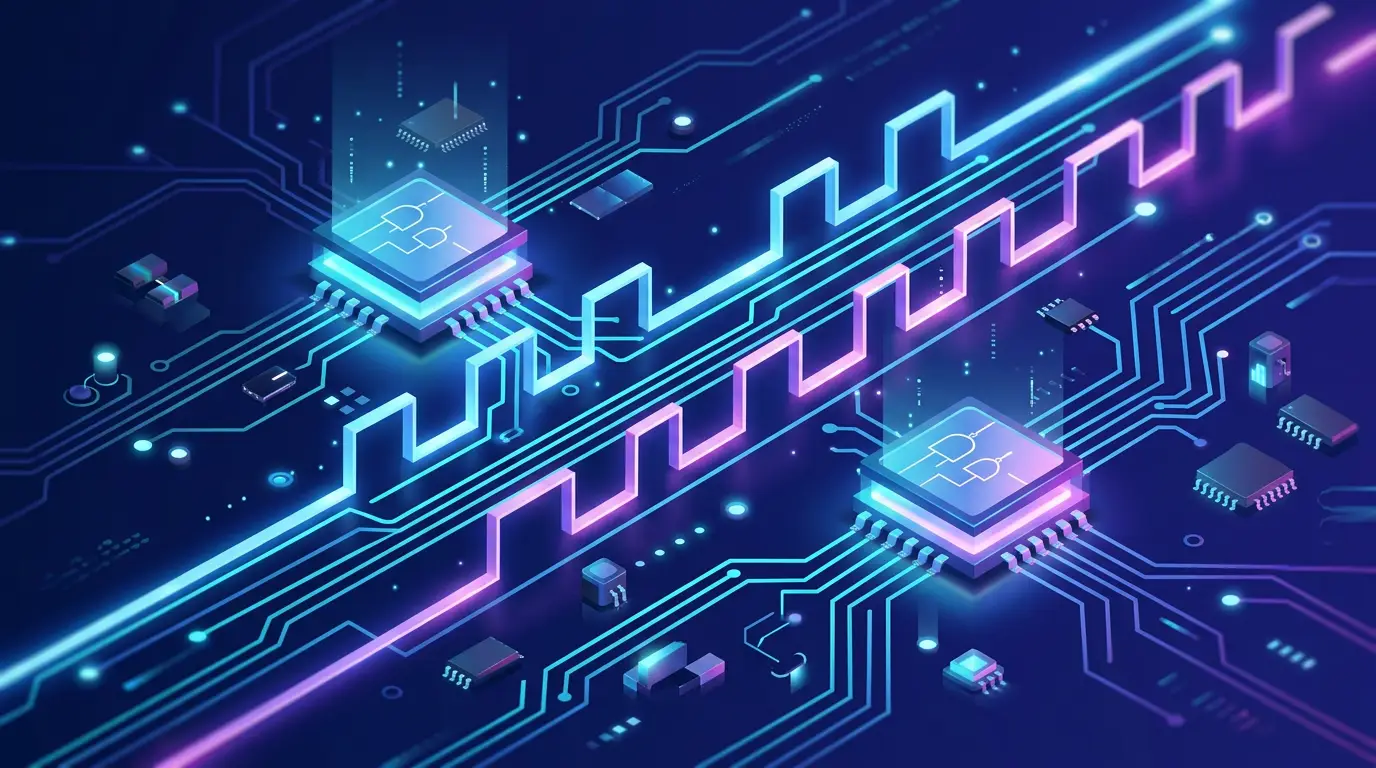

The Single-Bit Difference, in Hardware

If you draw both machines as block diagrams, the only difference is where the wire from “input” goes:

Mealy: Moore:

in ──┬──► next-state in ────► next-state

│ │ │

│ ▼ ▼

│ ┌──────┐ ┌──────┐

│ │ FFs │ │ FFs │

│ └──┬───┘ └──┬───┘

│ │ │

└──┬───┤ │

▼ ▼ ▼

┌────────┐ ┌────────┐

│ output │ ──► out │ output │ ──► out

│ logic │ │ logic │

└────────┘ └────────┘In the Mealy version, the input wire fans out to both the next-state logic and the output logic. In the Moore version, it only feeds the next-state logic; the output logic sees only the flip-flop outputs. That extra fan-out is the entire structural difference.

Worked Example 1: Traffic Light Controller

A simple intersection: north-south road and east-west road. Each direction has a Red/Yellow/Green light. There is one input — a sensor that detects a car waiting on the side road (car) — and the controller cycles through the standard four phases. We will build it in both styles.

The Phases

| Phase | NS light | EW light |

|---|---|---|

| 0 | Green | Red |

| 1 | Yellow | Red |

| 2 | Red | Green |

| 3 | Red | Yellow |

Transitions are timed by an external counter that pulses tick once per phase duration.

Moore Version

Four states, each with a fixed output. The transitions are simple:

| State | Output (NS, EW) | On tick go to |

|---|---|---|

| Green, Red | ||

| Yellow, Red | ||

| Red, Green | ||

| Red, Yellow |

Because the outputs only depend on state, the output logic is a 2-bit state-to-6-bit lookup. The encoding could be:

| State | Bits | NS_R | NS_Y | NS_G | EW_R | EW_Y | EW_G |

|---|---|---|---|---|---|---|---|

| 00 | 0 | 0 | 1 | 1 | 0 | 0 | |

| 01 | 0 | 1 | 0 | 1 | 0 | 0 | |

| 10 | 1 | 0 | 0 | 0 | 0 | 1 | |

| 11 | 1 | 0 | 0 | 0 | 1 | 0 |

The output logic is six DECODER-style minterm sums. With Karnaugh maps you can simplify each output expression — for instance, (the high state bit alone). The next-state logic is a simple 2-bit increment, identical to a counter. Light outputs are clean square waves.

Mealy Version with car Sensor

Now add the sensor. The rule: while in the green phase ( or ), if a car is detected on the cross street, transition to yellow immediately on the next tick regardless of how long we have been green. The car input gates the transition.

In a Mealy formulation we can also use the input to modify the output. For example, we can flash the corresponding green light for one cycle as a “vehicle acknowledged” signal:

| State | Input (tick, car) | Next state | Output |

|---|---|---|---|

| 0,0 | NS=Green, EW=Red | ||

| 0,1 | NS=Green+flash, EW=Red | ||

| 1,X | NS=Yellow, EW=Red | ||

| … | … | … | … |

Notice the output for state depends on car. That is the Mealy signature. The total number of states stays at 4 — we have packed the “car-detected, but it is not tick-time yet” behavior into the output logic instead of spawning a new state.

Comparison for the Traffic Light

| Aspect | Moore | Mealy (with sensor) |

|---|---|---|

| State count | 4 | 4 |

| Output stability | Solid (per cycle) | Glitches if car glitches |

Latency to react to car | 1 cycle | 0 cycles |

| Design verbosity | Higher (sometimes) | Lower (sometimes) |

For a real traffic light, Moore wins — you do not want the green light to flicker because a sensor wire bounces. For a packet protocol decoder where every cycle of latency costs throughput, Mealy often wins.

If you want to play with a Moore-style traffic light, the 4-bit counter with display template uses essentially this pattern, just driving a different output.

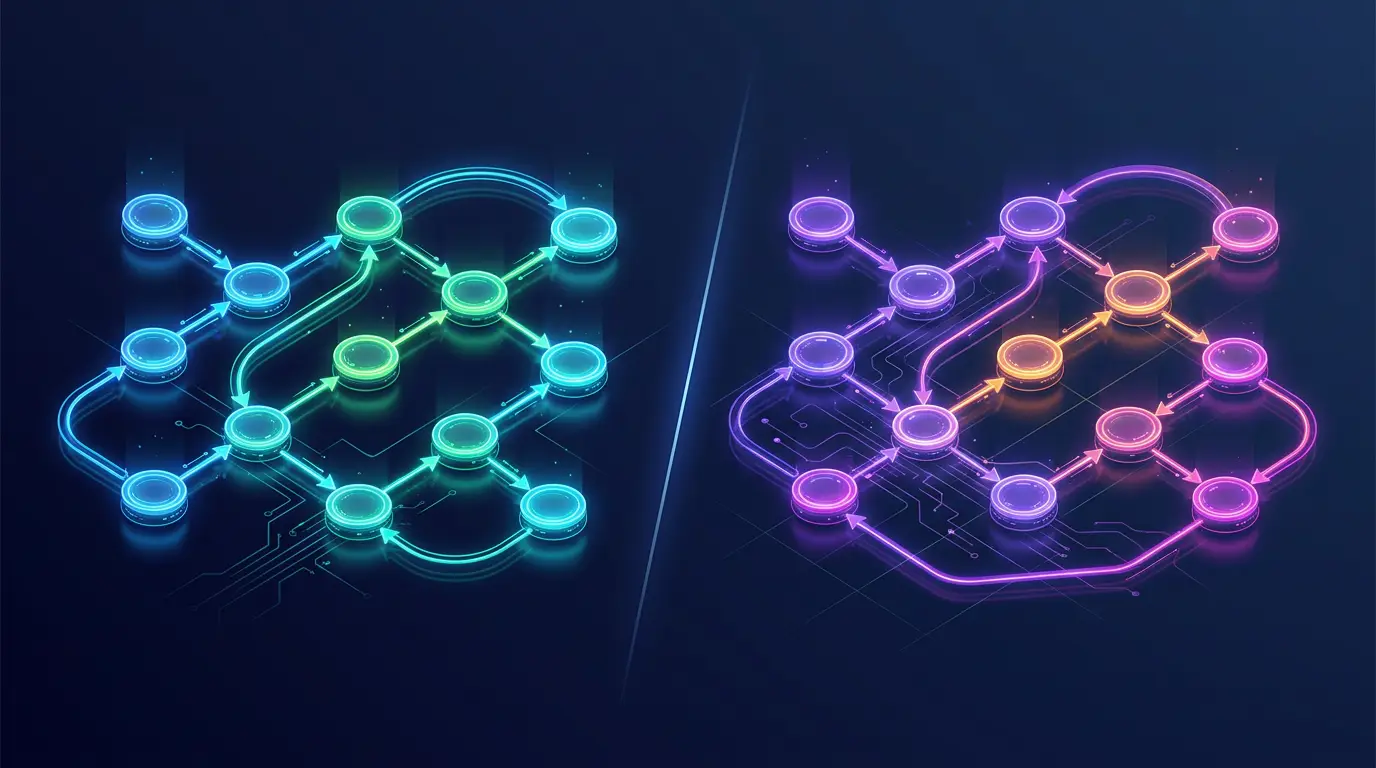

Worked Example 2: “1011” Sequence Detector

Both styles really earn their keep on the canonical FSM exercise: detect the bit pattern 1011 arriving serially on a single input, asserting a found output when the pattern completes. We allow overlapping matches — 10111011 matches twice.

Moore Detector

The Moore version needs five states: one for “last 0 bits matched,” one for “1 bit matched,” up to “4 bits matched (output HIGH).”

| State | Bits matched | Output |

|---|---|---|

| "" (nothing) | 0 | |

| ”1” | 0 | |

| ”10” | 0 | |

| ”101” | 0 | |

| ”1011” | 1 |

State transition table:

| Current | Input | Next | Output |

|---|---|---|---|

| 0 | 0 | ||

| 1 | 0 | ||

| 0 | 0 | ||

| 1 | 0 | ||

| 0 | 0 | ||

| 1 | 0 | ||

| 0 | 0 | ||

| 1 | 0 | ||

| 0 | 1 | ||

| 1 | 1 |

Five states need 3 flip-flops in binary encoding. The next-state logic is three combinational functions — one per state bit — derived from the table. K-map minimization for the LSB () of the next state, with as current state and in as input:

| in=0 | in=1 | |

|---|---|---|

| 000 () | 0 | 1 |

| 001 () | 0 | 1 |

| 010 () | 0 | 1 |

| 011 () | 0 | 0 |

| 100 () | 0 | 1 |

Reading off the K-map (don’t-cares for unused ): simplifies to a function of in and a couple of state bits, derivable using standard Boolean algebra techniques. The full simplification is exercise-grade; the structure is what we care about here.

The output logic is trivial: (the high bit, which is 1 only in when binary-encoded with ).

Mealy Detector

Mealy can do it with four states — one fewer.

| State | Bits matched | Transition | Next | Output on this transition |

|---|---|---|---|---|

| "" | 0 | 0 | ||

| "" | 1 | 0 | ||

| ”1” | 0 | 0 | ||

| ”1” | 1 | 0 | ||

| ”10” | 0 | 0 | ||

| ”10” | 1 | 0 | ||

| ”101” | 0 | 0 | ||

| ”101” | 1 | 1 |

Notice there is no . When we are in (“101 matched”) and the input is 1, we have just seen the full “1011” pattern — we assert found on that transition, and we move to (since the trailing “1” might be the start of the next overlapping match).

Four states fit in 2 flip-flops. The output logic is now (assuming encoding) — a single AND of three signals, but it is no longer purely a function of state.

Glitch Behavior

Imagine the input stream 1010111. In the Mealy detector, while we sit in , the found output combinationally tracks in. If in glitches HIGH for 5 ns and back LOW (a noisy wire, a metastable bit from an asynchronous source — the kind of thing covered in Mastering Setup, Hold, and Metastability), the found output glitches with it. A downstream counter that increments on found going HIGH will count a spurious match.

The Moore detector cannot exhibit this glitch. Its found output is a function of state only; the state cannot change between clock edges; therefore the output cannot change between clock edges.

Comparison for the Sequence Detector

| Aspect | Moore | Mealy |

|---|---|---|

| State count | 5 | 4 |

| Flip-flops (binary) | 3 | 2 |

| Match latency | 1 cycle | 0 cycles |

Output glitches on noisy in | No | Yes |

| Output logic | Trivial () | One AND |

If the sequence detector is part of a synchronous bus protocol decoder where the input is registered and stable, Mealy is excellent — you save a state and shave a cycle of latency. If the input is asynchronous from a noisy line, Moore is the safer choice.

Encoding: Binary vs One-Hot

Once you have settled on Mealy or Moore, the next decision is how to encode the states in flip-flops.

Binary Encoding

Use flip-flops for states. Five states = 3 flip-flops.

- Pro: Minimal flip-flops; smallest state register.

- Con: Next-state logic is more complex (more inputs feed each next-state bit). Output decoding is also a multi-bit AND.

One-Hot Encoding

Use one flip-flop per state. Five states = 5 flip-flops, only one of which is HIGH at any moment.

- Pro: Next-state logic is dramatically simpler — each state bit’s next value is just an OR of the conditions that lead to that state. Output decoding is free: the state bit is the output (Moore).

- Con: More flip-flops; illegal states (multiple bits HIGH) become possible.

When to Pick Which

| Constraint | Encoding |

|---|---|

| Few states, ASIC area-tight | Binary |

| Many states, FPGA (flip-flops are cheap) | One-hot |

| Need fast clock (logic depth matters) | One-hot (shorter logic paths) |

| Need clean output decoding | One-hot |

| Need formal verification of all states | One-hot (illegal states detectable) |

Most modern FPGA tools auto-encode states for you and will pick one-hot for state machines below ~16 states. ASIC flows tend to encode binary and re-time. Either way, the FSM’s behavior is independent of encoding — encoding is a mechanical choice you can leave to a synthesis tool.

Mealy vs Moore: The Decision Matrix

| Criterion | Mealy | Moore |

|---|---|---|

| State count | Fewer | More |

| Output latency | Same cycle as input | One cycle after input |

| Output stability | Can glitch with input | Stable for full cycle |

| Maximum clock frequency | Often lower (longer combinational path) | Often higher (output is just FF outputs) |

| Verification complexity | Higher (input × state combinations) | Lower (state alone) |

| Best for | Compact protocol decoders, pipeline control | Bus drivers, safety outputs, anything async |

The cleanest summary: Moore is conservative; Mealy is compact. Most production designs mix them — control paths that interface with external chips use Moore for clean timing, internal pipeline registers use Mealy to save area. There is no rule against mixing styles, and most real FSMs end up partly each.

Where State Machines Live in a Real CPU

The control unit of the CPU we built in Build a CPU from Scratch in a Simulator is a Moore machine. Each microstep is a state; each state’s output is a fixed bit-pattern of control wires (load enables, output enables, ALU op codes). The opcode in the IR feeds the next-state logic but does not combinationally affect the output — the output is a pure function of the microstep state.

This was a deliberate choice. The control wires drive the data bus and the tri-state buffers; a glitch on those wires would corrupt every register on the bus. Moore guarantees that within a single clock cycle, the control wires are rock-solid.

By contrast, the flag-checking logic for conditional branches is Mealy. The decision “should I take the JZ branch this cycle?” depends on both the microstep state and the current value of the Z flag — a combinational AND, exactly the Mealy pattern.

You will see the INSTRUCTION_REGISTER and REGISTER blocks at the heart of the register data transfer system template — that template has both Mealy and Moore patterns inside it, and is a useful one to inspect alongside this post. The upcoming Instruction Register and the Decode Stage post breaks the decode FSM down step by step, and the closely related CPU Flags Register post covers the Mealy flag-AND patterns.

Common Pitfalls

A few traps that catch first-time FSM designers:

- Forgetting unused-state recovery. With 3 flip-flops you have 8 possible states but only 5 used. If the state register ever lands in one of the 3 unused encodings (cosmic ray, power-on glitch, programmer error), the FSM may lock up. Design the next-state logic so that every unused state transitions to a known recovery state on the next clock — typically back to .

- Treating asynchronous inputs as synchronous. If your input crosses clock domains or comes from a button, register it through two flip-flops (a synchronizer) before letting it touch the FSM. Otherwise metastability will hand you intermittent failures.

- Mixing Mealy outputs with downstream Moore consumers. A Mealy output that glitches can drive a Moore receiver into the wrong state. If you must do this, register the Mealy output one cycle to flatten its glitches into the next clock period.

- Putting clock-gating logic in the next-state path. Combinational gates feeding into a clock pin are a path to misery. Use synchronous load-enables instead — the same pattern we used for the 4-bit register.

Try It Yourself

In DigiSim, build the four-state Mealy “1011” detector first — it is the smaller of the two and gives you the full FSM workflow in 30 minutes. Use a D_FLIP_FLOP pair for the state register, derive next-state and output equations from the transition table, and test with a serial input from an INPUT_SWITCH clocked by a CLOCK. Then build the Moore version with five states (3 flip-flops) and observe how the found output is delayed by one cycle relative to Mealy’s.

For a working sequential reference circuit that mixes both styles, open the register data transfer system template — its control logic is Moore, its data-path multiplexers are Mealy.

The two next-step posts that round out the FSM picture: Instruction Register and the Decode Stage shows a real CPU’s decode FSM drawn in both styles for comparison, and CPU Flags Register: Carry, Zero, Overflow, Sign walks through the Mealy AND-gates that gate conditional branches on flag values. Together with this post they cover the three FSMs you will encounter most often when reading a real CPU schematic.

The takeaway worth carrying forward: Mealy and Moore are not rival philosophies; they are two corners of a design space, and most real machines visit both. Pick Moore where output timing is load-bearing; pick Mealy where state count or latency is. Knowing which is which — and why — is a sign you are no longer reading FSMs as abstract diagrams and are starting to read them as circuits.