Using the Oscilloscope to Debug Digital Circuits

TL;DR: Drop an

OSCILLOSCOPE(2-channel) orOSCILLOSCOPE_8CH(8-channel) onto the canvas, wire each channel to the signal you care about, and run the simulation. The waveform window scrolls in real time, letting you see clock-to-Q delay on a flip-flop, catch a glitch in combinational logic, and confirm a clock is actually toggling at the rate you expect — all without leaving the browser.

Most timing bugs in digital circuits are invisible to the static schematic. A wire is high or low, but when it transitions matters more than what value it holds in steady state. The oscilloscope is the instrument for answering “when?”, and DigiSim ships two flavors of it as first-class components on the canvas.

This guide walks through placing an oscilloscope, hooking it up, and reading three real waveforms: a clock signal, a D flip-flop’s clock-to-Q delay, and a static-1 hazard on a combinational output. By the end you’ll know which knobs matter, what each pattern looks like on screen, and when to reach for the 8-channel variant instead of the 2-channel one.

What does the OSCILLOSCOPE component actually show?

In DigiSim, the oscilloscope is a virtual logic analyzer. It samples each connected wire at every simulation tick and plots the result as a stepped waveform on a scrolling time axis. There are two variants:

OSCILLOSCOPE— two input channels. Use it when you want to compare two signals, the most common case being clock vs data.OSCILLOSCOPE_8CH— eight input channels. Use it for a parallel bus, a register’s output bits, or a state machine whose state and inputs you want side by side.

Both share the same display: a horizontal time axis that scrolls left as the simulation advances, and a stack of horizontal traces (one per channel) drawn as 0/1 step lines. The component documentation pages — /docs/OSCILLOSCOPE and /docs/OSCILLOSCOPE_8CH — list every input pin and configuration option.

A scope does not change circuit behavior. It is a passive observer. You can connect or disconnect a channel mid-simulation without disturbing anything else on the canvas.

Step 1: Place a scope on the canvas

Open any circuit — a blank one is fine — and drag OSCILLOSCOPE from the component palette onto the canvas. The component renders as a rectangular block with two input pins on the left labelled CH1 and CH2, and a wide display area on the right showing a flat baseline.

If you need more than two signals, drag OSCILLOSCOPE_8CH instead. It looks identical except it has eight input pins stacked on the left edge and eight stacked traces on its display.

A useful pattern: put the scope below or to the right of the logic it’s measuring, so the waveform area has horizontal room to scroll. The scope display widens with the component, and a wider scope shows more history before it scrolls events off the left edge.

Step 2: Wire channels to the signals you want to watch

Click on the wire you want to probe and drag a connection from it to the scope’s CH1 input. The wire keeps doing its normal job — driving whatever it was already driving — and the scope just listens.

A standard hookup for sequential logic looks like this:

CH1to the clock wire (the output of aCLOCKcomponent)CH2to the data signal you want to compare against the clock (a flip-flop’sQ, a register’s bus bit, a state-machine output)

For an 8-channel scope on a 4-bit register, wire CH1–CH4 to the four data bits and use CH5 for the clock and CH6 for the enable line. That gives you the entire register’s behavior on one pane.

Hook up the d-latch-with-oscilloscope template to see a working example without building from scratch — it ships with the scope pre-wired to the latch’s clock and data lines.

Step 3: Run, pause, and step the simulation

Press the run/play control. The simulation starts ticking and the scope’s display begins to scroll. Each rising and falling edge shows up as a vertical transition on the corresponding trace.

Two controls matter for debugging:

- Pause. Freezes the display so you can study a specific moment. The waveform stops scrolling but stays visible. Wires still show their current logic level.

- Step. Advances the simulation by a single tick. Use it to walk through an edge transition one increment at a time. Useful when you want to see exactly what value a signal had on the cycle before a clock edge.

A common workflow: let the simulation run until you see the waveform you’re suspicious of, hit pause, then step backwards mentally by reading the trace from right to left. The scope shows past events, so the rightmost edge is “now” and everything to the left is history.

Use case 1: verify a clock signal

Before you debug anything else, sanity-check the clock. A surprising number of “the flip-flop isn’t latching” bugs are actually “the clock isn’t running at all” or “the clock is running but at half the frequency I configured.”

Drop a CLOCK component, set its period (say, 100 ticks high, 100 ticks low), and connect its output to CH1 of a 2-channel scope. Run the simulation.

You should see a clean square wave: the trace sits at 0 for 100 ticks, jumps to 1, sits there for 100 ticks, drops back to 0, repeating. If the trace is flat, the clock isn’t enabled. If the period looks wrong, double-check the duty cycle and period parameters in the clock’s properties panel.

For a deeper treatment of why every synchronous design needs a clock, see the clock pulse: why computers need a heartbeat.

Use case 2: see a D flip-flop’s clock-to-Q delay

The defining behavior of a D flip-flop is that Q only changes on a clock edge. The oscilloscope makes this concrete.

Build the standard hookup:

CLOCK→ flip-flopCLK→ scopeCH1- An input switch → flip-flop

D→ scopeCH2is also useful, but for the first run, only watch the clock andQ - Flip-flop

Q→ scopeCH2

Toggle the D input a few times manually so it’s high. Run the simulation.

On the scope you’ll see the clock toggling on CH1. On CH2, Q only transitions on the rising edge of the clock — never on the falling edge, never between edges. If you flip D low while the clock is in the middle of a high half-cycle, nothing happens to Q until the next rising edge. That delay between the clock edge and the corresponding Q change is the clock-to-Q propagation delay, and it’s the single most important number for figuring out how fast a synchronous circuit can run.

Propagation delay is what budgets timing in real CPUs. The scope is the tool that lets you measure it for any flip-flop or combinational chain in your circuit.

The same hookup works for the JK flip-flop master-slave template — drop a scope onto it and watch the master and slave latch on opposite clock phases.

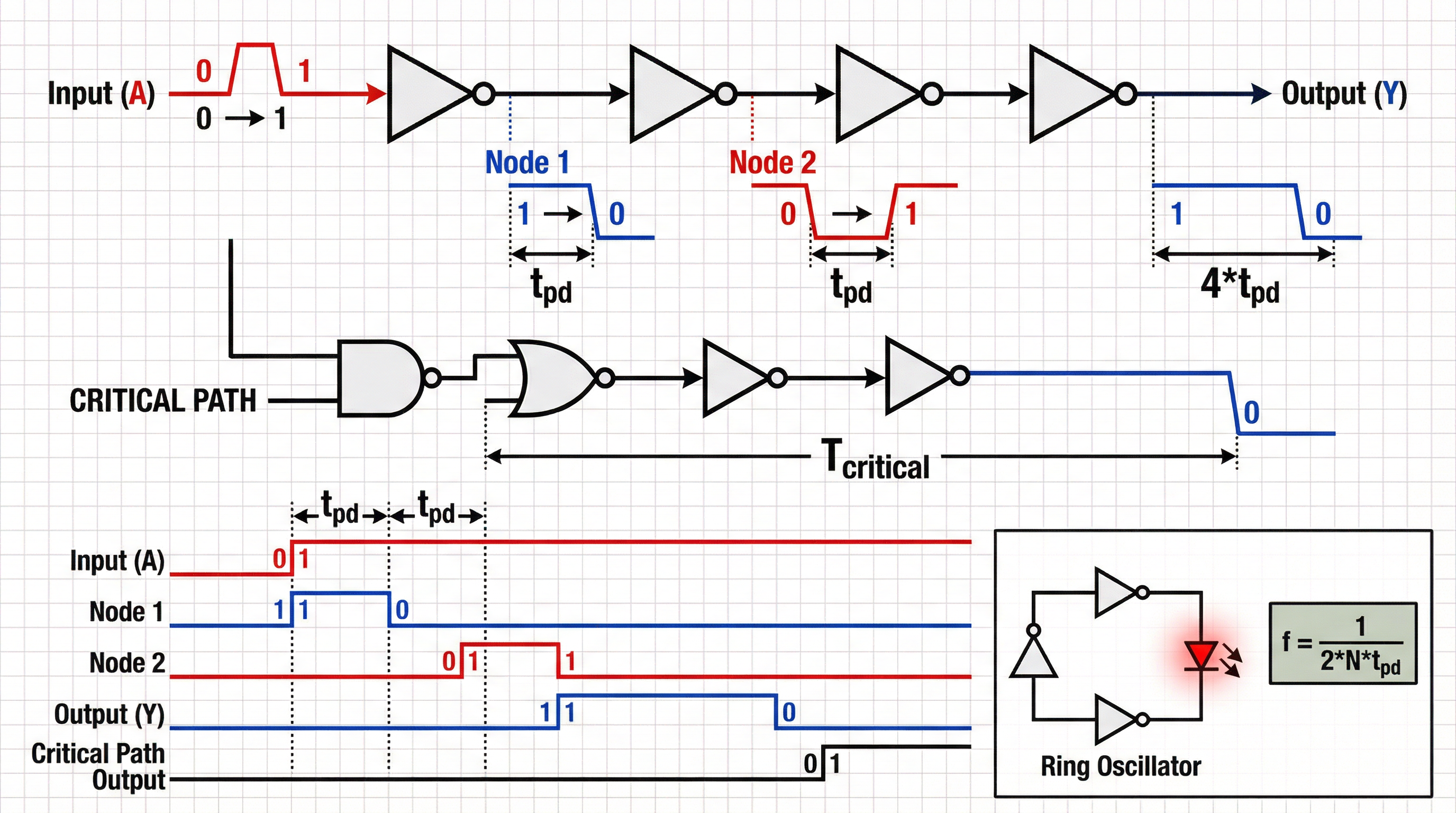

Use case 3: spot a glitch in combinational logic

Combinational hazards are the most frustrating class of digital bug because the steady-state truth table is correct. The output is right after things settle. The problem is that during the transition between two correct steady states, the output briefly takes a wrong value.

Build a simple hazard demonstrator:

- Two

ANDgates feeding anORgate (a 2-input multiplexer-like topology) - A select line whose change should leave the output unchanged for a particular input combination

- Scope

CH1on the select line,CH2on theORoutput

When you toggle the select line, the OR output should hold steady at 1. Run the simulation, watch the scope.

A static-1 hazard appears as a brief dip from 1 to 0 and back to 1 on the output trace, lasting one or two simulation ticks, immediately after the select line transitions. The trace looks like the output “blinked off” momentarily. In a real circuit, that blink can clock a downstream flip-flop unintentionally.

If you don’t see a glitch, congratulations — your topology happens to be hazard-free for that input. If you do see one, the standard fix is a redundant gate that covers the transition: classic Karnaugh-map territory.

We’ll dig deeper into hazards in an upcoming post on static-vs-dynamic hazards in combinational logic. For now, the takeaway is: the scope makes hazards visible. Without it, you’d never notice a one-tick glitch.

Reading the time axis

Each horizontal pixel on the scope corresponds to one or more simulation ticks, depending on how zoomed-in the display is. The grid behind the traces is your time reference. Count grid divisions between two edges to estimate intervals.

For tight timing measurements — clock-to-Q delay, propagation delay through a gate chain — pause the simulation when the event of interest is on screen, then count ticks from the causing edge to the resulting edge. If your circuit’s gates each have a one-tick delay, a chain of three gates between a flip-flop’s Q and a downstream input adds three ticks.

This is exactly the budget you need to track when worrying about setup and hold time and metastability. Setup violations show up on the scope as a Q change that almost aligns with the clock edge — the data line transitioned within the setup window, and the flip-flop’s output is now indeterminate. Catching that pattern visually beats waiting for the bug to bite in production.

We’ll cover one more related effect — clock skew and its effect on timing — in an upcoming post. The short version: when the same clock arrives at two flip-flops at slightly different times, an 8-channel scope wired to both clock inputs will show the gap directly.

When to use 8 channels instead of 2

Reach for OSCILLOSCOPE_8CH whenever you’re debugging:

- A multi-bit bus (a 4-bit register’s output, an 8-bit ALU result)

- A state machine where you want to see the current state encoding alongside the inputs

- Two or more flip-flops on the same clock, where you want to confirm their

Qoutputs change together - A pipeline where data should advance one stage per clock cycle

The 2-channel version is enough for most flip-flop level work. Step up to the 8-channel when the question is “are these signals in sync?” rather than “what does this signal look like?”

Tips that save time

- Label your channels. Put a text annotation next to the scope describing which wire each channel measures. After 20 minutes of debugging, you will not remember.

- Wire the clock to the same channel every time. Pick a convention — say, always

CH1for clock — and stick to it. Your eye learns to read traces faster. - Pause before reading. A scrolling display is hard to study. Pause, then trace edges from the cause (clock) to the effect (

Q). - Use one scope per logical group. Don’t overload one 8-channel scope with unrelated signals. Two 2-channel scopes, each focused on a subsystem, are easier to read.

- Step through clock edges. If you’re investigating a single edge, the step control gives you a tick-by-tick view of what each signal does immediately before, during, and after the transition.

Where to go next

Once the oscilloscope is part of your default workflow, the rest of digital debugging gets dramatically faster. You stop arguing about “is this signal right?” and start measuring it.

A natural follow-up is the unseen clock: mastering setup, hold, and metastability — every concept in that post becomes visible on a scope trace. If you’re still building intuition for what a clock is and why every flip-flop needs one, start with the clock pulse: why computers need a heartbeat.

Ready to try it? Open the d-latch-with-oscilloscope template and watch a real latch’s transparent and hold phases on the scope — no setup required.