디코더

개요

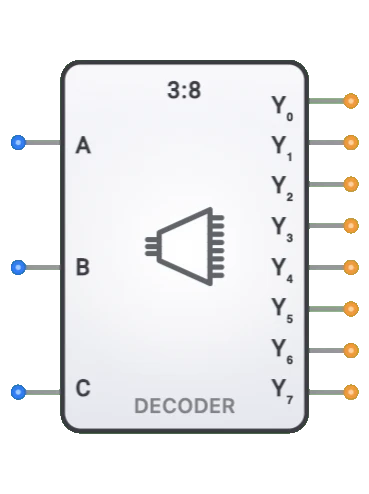

- 목적: 디코더는 이진 코드 입력을 개별 출력 라인의 집합으로 변환하는 조합 논리 회로로, 각 고유한 입력 코드에 대해 하나의 출력만 활성화됩니다. 간결한 이진 표현을 "원-핫" 형식으로 확장합니다.

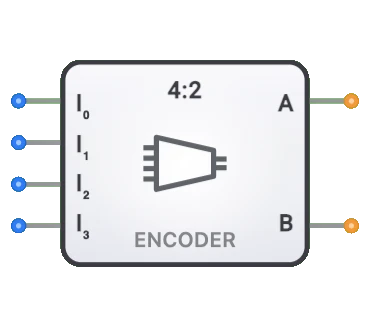

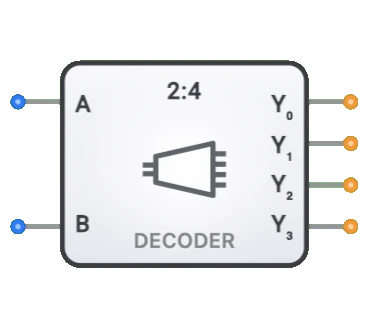

- 기호: DigiSim.io에서의 디코더는 2개의 이진 입력 라인(A0, A1)과 4개의 출력 라인(Y0, Y1, Y2, Y3)이 있는 직사각형 블록으로 표현되는 2대4 디코더입니다.

- DigiSim.io 역할: 디지털 회로에서 주소 디코딩, 데이터 라우팅 및 제어 신호 생성을 위한 기본 빌딩 블록으로 사용됩니다.

기능 설명

논리 동작

디코더는 입력에 있는 이진 값에 따라 정확히 하나의 출력 라인을 활성화합니다. 이진 입력 조합에 해당하는 출력만 HIGH가 되고, 다른 모든 출력은 LOW로 유지됩니다.

진리표 (2대4 디코더):

| A1 | A0 | Y0 | Y1 | Y2 | Y3 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

입력 및 출력

입력:

- 주소 입력(A0, A1): 어떤 출력이 활성화될지를 결정하는 2개의 이진 입력.

출력:

- 출력 라인(Y0-Y3): 4개의 출력 라인으로, 각 고유한 입력 조합에 대해 하나의 출력만 활성(HIGH)입니다.

구성 가능한 매개변수

- 활성 레벨: 출력이 활성 하이(1)인지 활성 로우(0)인지 여부.

- 전파 지연: 입력 변경 후 출력이 변경되는 데 걸리는 시간.

DigiSim.io에서의 시각적 표현

디코더는 왼쪽 또는 하단에 2개의 입력 핀(A0, A1)과 오른쪽 또는 상단에 4개의 출력 핀(Y0-Y3)이 있는 직사각형 블록으로 표시됩니다. "2:4" 크기 표기로 라벨이 지정됩니다. 회로에 연결되면 구성 요소는 연결 와이어의 색상 변화를 통해 어떤 출력이 활성인지 시각적으로 나타냅니다.

교육적 가치

핵심 개념

- 이진 인코딩/디코딩: 이진 값이 원-핫 표현으로 확장될 수 있는 방법을 보여줍니다.

- 주소 선택: 이진 주소가 특정 메모리 위치 또는 장치를 선택하는 데 사용되는 방법을 설명합니다.

- 원-핫 인코딩: 여러 가능한 신호 중 하나만 활성인 개념을 소개합니다.

- 조합 논리 설계: 기본 논리 요소로 복잡한 기능을 구현하는 방법을 보여줍니다.

학습 목표

- 이진 값이 개별 선택 라인으로 디코딩되는 방법을 이해합니다.

- 디코더가 디지털 시스템에서 효율적인 주소 지정을 가능하게 하는 방법을 학습합니다.

- 메모리 시스템 및 제어 장치에서 디코더의 역할을 인식합니다.

- 주소 디코딩 회로 및 제어 신호 생성기 설계에 디코더를 적용합니다.

- 디코더를 캐스케이드하여 더 큰 디코딩 구조를 만드는 방법을 이해합니다.

사용 예시/시나리오

- 메모리 주소 지정: 주소 비트에 따라 특정 메모리 칩 또는 메모리 위치 선택.

- 명령어 디코딩: 프로세서에서 명령어 연산 코드에 따라 제어 신호 생성.

- 입출력 선택: 주소 값에 따라 특정 주변 장치 활성화.

- 디스플레이 구동: 디스플레이 시스템에서 이진 값을 세그먼트 패턴으로 변환.

- 상태 디코딩: 상태 머신에서 현재 상태에 따라 특정 제어 신호 생성.

기술 참고사항

- DigiSim.io 디코더는 2개의 입력(A0, A1)과 4개의 출력(Y0-Y3)을 가진 2대4 디코더입니다.

- 디코더에서 입력(n)과 출력(m)의 관계는 일반적으로 m = 2^n입니다.

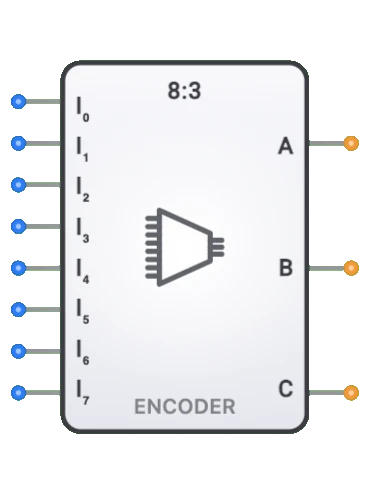

- 디코더를 캐스케이드하여 더 큰 디코더를 만들 수 있습니다. 예를 들어, 두 개의 2대4 디코더와 추가 입력으로 3대8 디코더를 만들 수 있습니다.

- 활성 로우 디코더에서 출력은 일반적으로 HIGH이며 선택 시 LOW가 되는데, 이는 메모리 칩 선택 애플리케이션에서 자주 사용됩니다.

- DigiSim.io에서 디코더는 입력 변경에 즉시 응답하여 이러한 구성 요소의 조합 논리 동작을 모델링합니다.

디코더의 종류

이진 디코더

- 표준 n대2^n 디코더(예: 2대4, 3대8, 4대16)

- 이진 코드를 원-핫 출력으로 변환

BCD-십진수 디코더

- BCD를 십진수 디스플레이로 변환하는 4대10 디코더

- 디스플레이 애플리케이션에서 일반적

주소 디코더

- 메모리 및 I/O 주소 선택에 사용

- 종종 칩 선택 출력 포함

7세그먼트 디스플레이 디코더

- 이진/BCD 입력을 7세그먼트 디스플레이 출력으로 변환

- 숫자 디스플레이를 위한 4대7 디코더

디멀티플렉서

- 데이터 라우팅에 사용되는 디코더의 특수한 경우

- 하나의 입력을 여러 출력 중 하나로 라우팅

활성 로우 디코더

- 출력이 일반적으로 하이이며 활성 출력이 로우로 변함

- 메모리 시스템에서 자주 사용

응용

메모리 주소 디코딩

- 올바른 메모리 칩 또는 메모리 위치 선택

- 메모리 시스템에서의 칩 선택 생성

명령어 디코딩

- CPU에서 제어 신호 생성

- 연산 코드 해석

데이터 라우팅

- 적절한 처리 장치로 데이터 전달

- 마이크로프로세서에서의 버스 주소 지정

디스플레이 시스템

- 7세그먼트 디스플레이 구동

- LCD/LED 매트릭스 제어

키보드/키패드 스캐닝

- 매트릭스 키보드 스캐닝

- 입력 장치 제어

디멀티플렉싱 연산

- 통신 시스템에서의 신호 라우팅

- 채널 선택

제어 신호 생성

- 명령어 코드에 따라 특정 제어 신호 생성

- 상태 머신 출력

구현 방법

논리 게이트 배열

- 필요에 따라 입력 인버터가 있는 AND 게이트

- 종종 트리 구조로 배열

집적 회로

- 74LS138: 3대8 디코더

- 74LS154: 4대16 디코더

- 74LS47: BCD에서 7세그먼트 디코더

NAND/NOR 게이트 구현

- 모든 디코더 기능을 위한 범용 게이트 사용

- 일반적으로 AND/OR보다 적은 게이트 필요

HDL 설계

- Case 문 또는 조건부 할당 사용

- 다양한 크기로 쉽게 매개변수화

ROM 기반 구현

- 복잡한 디코더 기능을 위한 룩업 테이블 사용

- 프로그래머블 논리 접근 방식

회로 구현 (2:4 디코더)

간단한 2대4 디코더는 인버터가 있는 AND 게이트를 사용하여 구현할 수 있습니다:

graph LR

InputA0[A0] --> NotGate0[NOT]

InputA1[A1] --> NotGate1[NOT]

NotGate0 --> AndGate0[AND]

NotGate1 --> AndGate0

AndGate0 --> OutputY0[Y0: 00]

InputA0 --> AndGate1[AND]

NotGate1 --> AndGate1

AndGate1 --> OutputY1[Y1: 01]

NotGate0 --> AndGate2[AND]

InputA1 --> AndGate2

AndGate2 --> OutputY2[Y2: 10]

InputA0 --> AndGate3[AND]

InputA1 --> AndGate3

AndGate3 --> OutputY3[Y3: 11]

출력 선택: 각 출력은 고유한 2비트 주소 조합에 대응합니다.

부울 표현식 (2:4 디코더)

2대4 디코더의 경우:

- Y0 = Ā1 · Ā0

- Y1 = Ā1 · A0

- Y2 = A1 · Ā0

- Y3 = A1 · A0

여기서 ·는 논리 AND를, Ā는 논리 NOT을 나타냅니다

관련 구성 요소

- 인코더: 역방향 연산 수행(원-핫에서 이진으로)

- 멀티플렉서: 선택 라인에 따라 여러 입력 중 하나를 선택

- 디멀티플렉서: 기능적으로 유사하지만 패턴 생성 대신 데이터 라우팅

- 우선순위 인코더: 여러 활성 입력을 처리하는 특수 인코더

- 디스플레이 드라이버: 디스플레이 제어를 위한 디코더를 종종 포함

- 메모리 주소 디코더: 메모리 시스템에 특화

- 프로그래머블 논리 배열: 디코더 기능 구현 가능