Demultiplexer Tutorial: 1-to-4 and 1-to-8 (DEMUX)

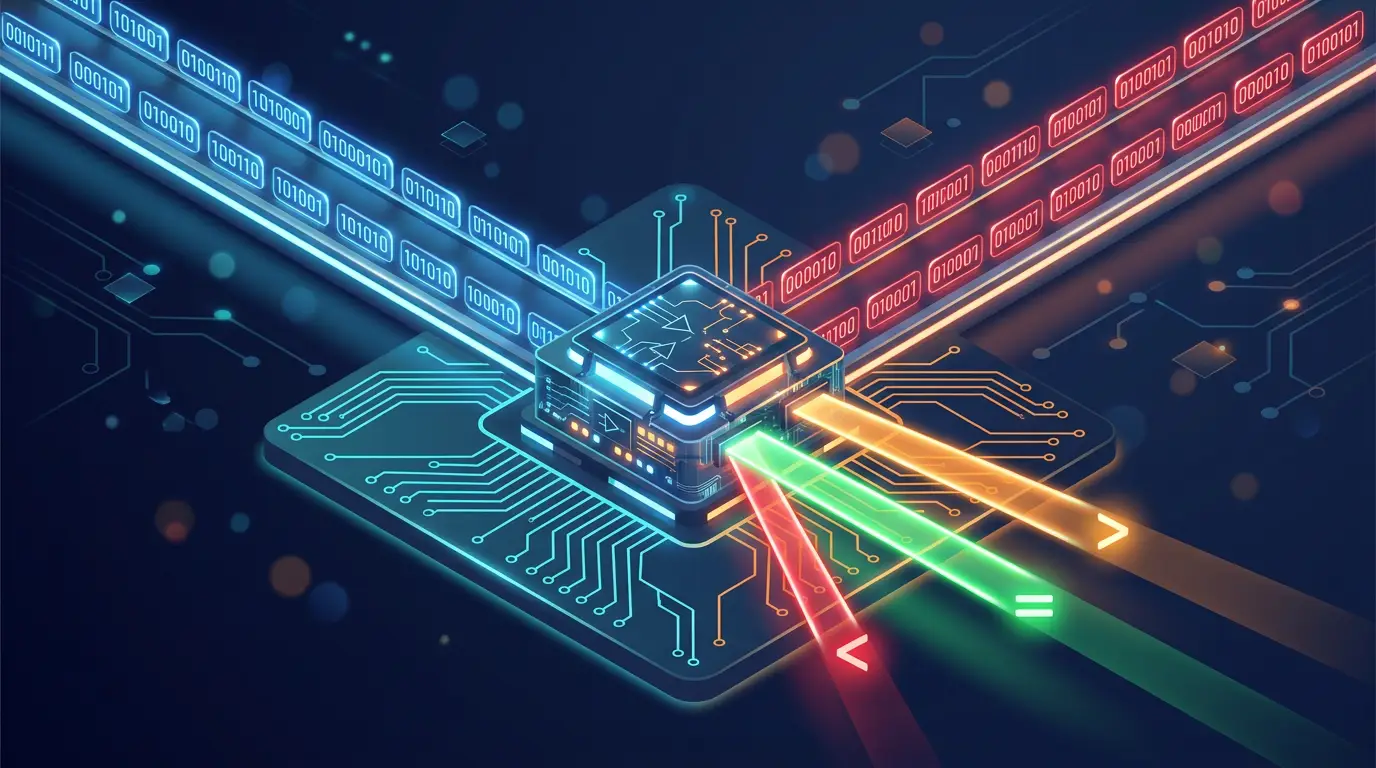

TL;DR: A demultiplexer (DEMUX) is a combinational circuit that takes one data input and routes it to one of output lines, with the destination chosen by an n-bit select code. All non-selected outputs are held at 0. A DEMUX is functionally a decoder whose enable input has been replaced by the data input.

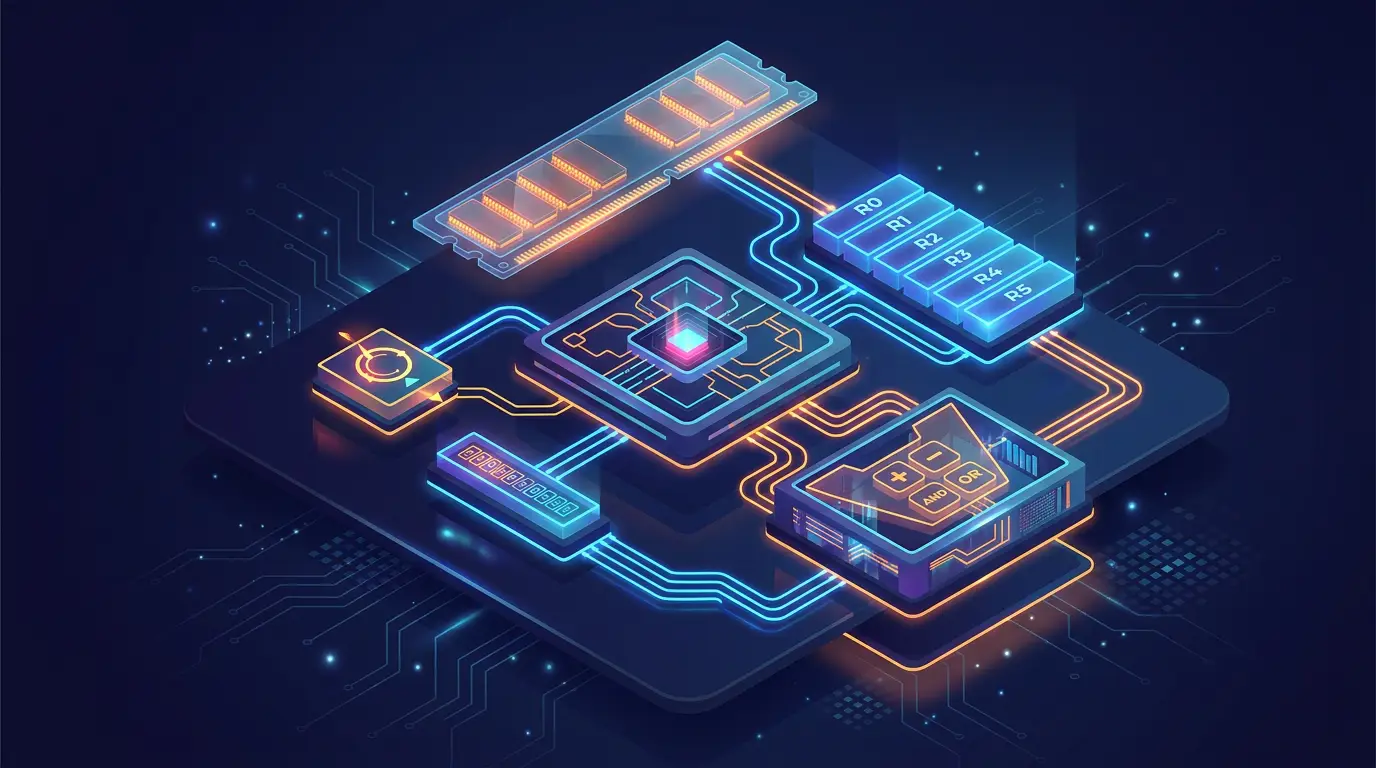

The demultiplexer is the inverse of the multiplexer: a multiplexer picks one of many inputs to drive one output, while a demultiplexer takes one input and steers it to one of many outputs. Inside a CPU, DEMUX logic decides which register receives the bus value on a write, which memory bank receives a strobe, and which functional unit receives a clock pulse on a given cycle. Like the multiplexer, the demultiplexer turns a bundle of wires into a single addressable channel — and that addressability is what makes register files, memory hierarchies, and instruction dispatch possible.

What is a demultiplexer?

A demultiplexer is a combinational circuit with one data input D, n select inputs , and output lines . The output addressed by the binary value of S equals D; every other output is 0. Symbolically:

where is the i-th minterm of the select inputs — that is, the AND of the select bits in the appropriate polarity to produce a 1 only when S = i.

This formulation makes the relationship to a decoder explicit: a decoder produces on each output line . A demultiplexer produces . Replace the decoder’s enable input with D, and the decoder becomes a demultiplexer. The 74139 IC (dual 2-to-4 decoder/demultiplexer) and the 74138 IC (3-to-8 decoder/demultiplexer) are sold as both, because the same silicon does both jobs.

For the multiplexer counterpart and the broader pair, see Multiplexers Demystified: The Data Traffic Controller.

The 1-to-2 demultiplexer

The smallest useful DEMUX has one data input, one select input, and two outputs:

| S | D | Y1 | Y0 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 |

The boolean equations:

Two AND gates and one inverter — that is the entire circuit. The pattern generalizes: each output is D ANDed with the appropriate minterm of the select inputs.

The 1-to-4 demultiplexer

Two select bits give four outputs:

| S1 | S0 | Y3 | Y2 | Y1 | Y0 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | D |

| 0 | 1 | 0 | 0 | D | 0 |

| 1 | 0 | 0 | D | 0 | 0 |

| 1 | 1 | D | 0 | 0 | 0 |

Boolean equations:

Four 3-input ANDs and two inverters. Each AND output is exactly one of the four minterms of gated by D.

The structural similarity to a 2-to-4 decoder is the foundation of an alternative implementation: take a 2-to-4 decoder, which produces the four minterms on its outputs, and AND each minterm with D. The result is a 1-to-4 demultiplexer. This is the path most physical layouts take, because a decoder block is reusable elsewhere on the chip — see Decoders and Encoders: Driving a 7-Segment Display for the decoder side. The AND primitive that gates D into each output line is covered in The AND Gate: Foundation of Digital Logic.

A standalone block is at /docs/DEMULTIPLEXER_1TO4; the toggleable simulator model is at /template/1-to-4-demultiplexer.

The 1-to-8 demultiplexer

Three select bits give eight outputs. The truth table doubles in height; each row sets a single to D and the other seven to 0. The general equation:

where is the j-th bit of i and , . In plain English: each output is D ANDed with the minterm corresponding to its index. Eight 4-input ANDs and three inverters realize the entire function.

The 74138 IC implements this with active-low outputs (so the selected output goes to 0 and the others stay at 1) and three enable inputs that all must be in the right state to allow any output to assert. The active-low convention is convenient for chip-select fanout in memory systems — a typical use case where the DEMUX selects which RAM chip receives a read strobe.

The DigiSim model lives at /docs/DEMULTIPLEXER_1TO8 with the simulator template at /template/1-to-8-demultiplexer. The smaller 1-to-2 case is at /template/1-to-2-demultiplexer and the parent block at /docs/DEMULTIPLEXER.

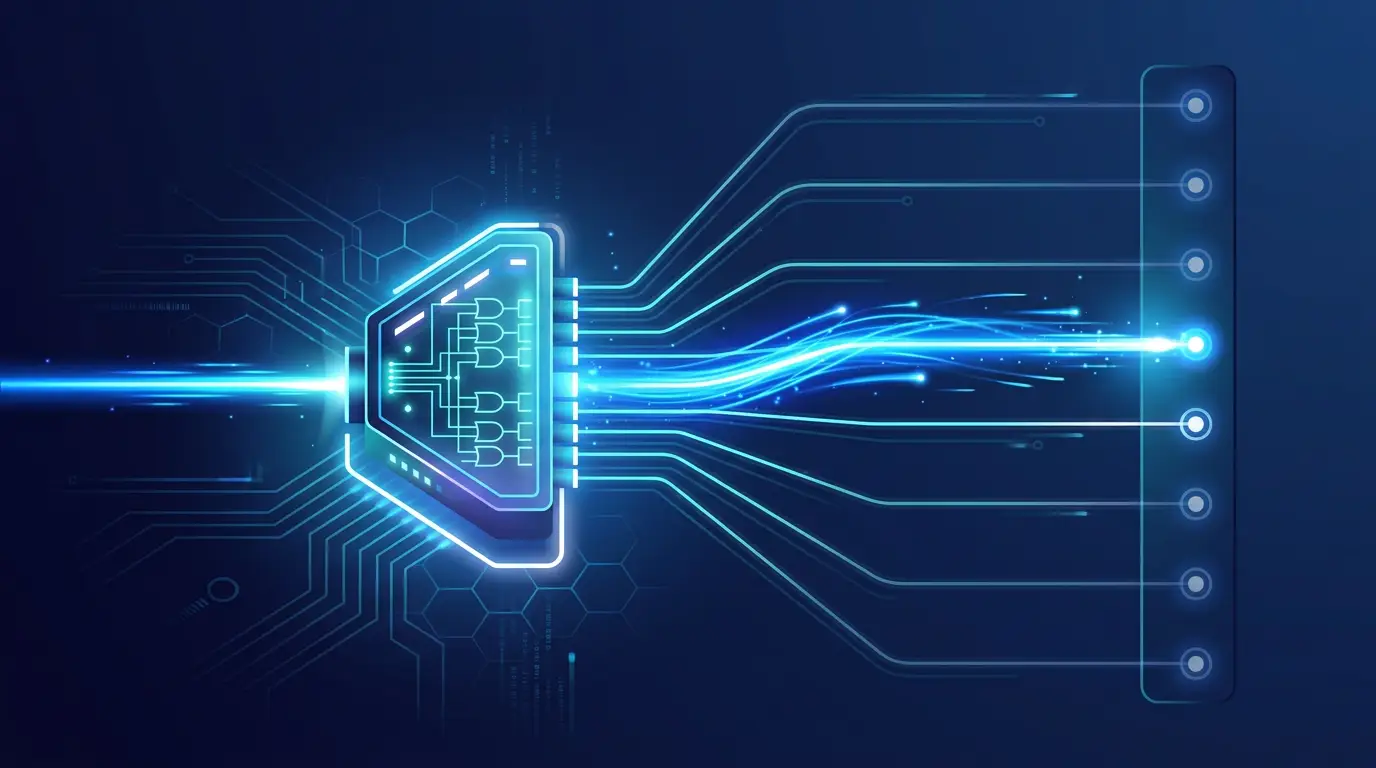

DEMUX from a decoder + AND

A practical implementation route — and often the cheapest in modern silicon — is to take an existing decoder and AND each of its outputs with the data input. For a 1-to-8 DEMUX:

S2,S1,S0 ──► 3-to-8 decoder ──► 8 minterm lines m0..m7

D ──┐

├── AND ── Y0 (D AND m0)

├── AND ── Y1 (D AND m1)

...

└── AND ── Y7 (D AND m7)If the decoder already exists for another purpose (instruction decoding, address decoding), the marginal cost of the DEMUX is just the eight AND gates. This is one reason CPU layout teams prefer to factor decoder logic out and reuse it across multiple DEMUX-shaped functions on the chip.

Use case 1: register file write port

A CPU register file has many registers and one (or a few) write ports. On every cycle, at most one register is written. The mechanism is a DEMUX: the destination register index from the instruction’s destination field drives the select input, the result bus from the ALU drives the data input, and the DEMUX outputs are wired to the write-enable signals of each register. Only the addressed register sees its enable assert; all others ignore the cycle.

For a 16-register file, this is a 1-to-16 DEMUX (or two 1-to-8 DEMUXes cascaded). For a 32-register file (RISC-V’s RV32I, ARM’s general-purpose register set), it is a 1-to-32. The structure is the same; the width differs.

Use case 2: clock and strobe distribution

A clock-gating tree uses DEMUX logic to deliver a clock pulse to one of several functional units per cycle. A select code from the control unit picks the destination, the clock signal feeds D, and the chosen output toggles. Non-selected outputs stay at 0, holding their downstream registers static and saving power.

The same idea applies to memory write strobes. A memory bank has a single shared write strobe driven by the CPU; a DEMUX (often integrated into the address decoder) picks which bank receives it on this cycle. Banks not selected ignore the data on the bus, and only the addressed bank latches the new value.

Use case 3: serial-to-parallel routing and audio switching

A 1-to-N DEMUX combined with a counter implements serial-to-parallel routing: the counter scans the select inputs, and each bit of a serial stream is routed to a different output. With a hold register on each output, this becomes a 1-to-N demultiplexed write — useful for fanning a single sensor or display channel out to several parallel destinations.

In analog form, the same structure routes audio. A “DEMUX” mode on a stereo receiver picks which speaker pair receives the active source. The select code is set by a front-panel control; the rest is the same digital topology, with analog switches replacing AND gates.

DEMUX vs decoder: when to use which

The two blocks are dual-purpose silicon, but the language differs:

| Term | Inputs | Outputs | Typical use |

|---|---|---|---|

| Decoder | n select + 1 enable | minterm lines | Address decoding, opcode decoding |

| DEMUX | n select + 1 data | data lines | Register write port, clock distribution |

If the input being routed is just an enable, the block is being used as a decoder. If the input being routed carries actual data, the block is being used as a demultiplexer. The IC is the same; the role differs.

Build it and route a single bit

Start with the 1-to-4 case at /template/1-to-4-demultiplexer and walk through the four select positions while toggling D — only one output follows D on each setting, the others stay at 0. Then move to /template/1-to-8-demultiplexer for the wider version. The DEMUX really clicks the moment it is wired into a write port: pick a register, feed the bus into D, watch only that register update. The same structure underlies the CPU flags register, where a small DEMUX-shaped network decides which flag bits update on each ALU operation.