The SR Latch: Unpacking the Fundamental Building Block of Digital Memory

In the silent, clockwork universe of digital logic, every complex operation—from a processor executing billions of instructions per second to a graphics card rendering a photorealistic world—boils down to manipulating ones and zeros. But how does a circuit remember a one or a zero? The answer lies not in a complex microprocessor, but in one of the most elegant circuits ever conceived: the Set-Reset Latch, or SR Latch.

This simple arrangement of two cross-coupled logic gates is the first rung on the ladder of sequential logic. It is the most basic form of memory, the digital equivalent of a single neuron holding a state. Understanding the SR Latch means grasping the very essence of how digital systems store information.

What is an SR Latch?

At its core, an SR Latch is a bistable circuit, meaning it has two stable states. It can be instructed to enter one of these states and will remain there—or “latch”—until told to change. This ability to hold a value is what separates it from combinational logic (like AND or OR gates), whose outputs depend solely on their current inputs.

The latch has two inputs, conventionally named S (Set) and R (Reset), and typically two outputs, Q and its complement, .

- Set (S): When activated, this input forces the Q output to a logic ‘1’.

- Reset (R): When activated, this input forces the Q output to a logic ‘0’.

- Hold: When neither S nor R is active, the latch maintains its last state indefinitely. This is the “memory” feature.

There are two primary implementations of the SR Latch, each built from a different gate type. Let’s explore both, starting with the NOR gate version.

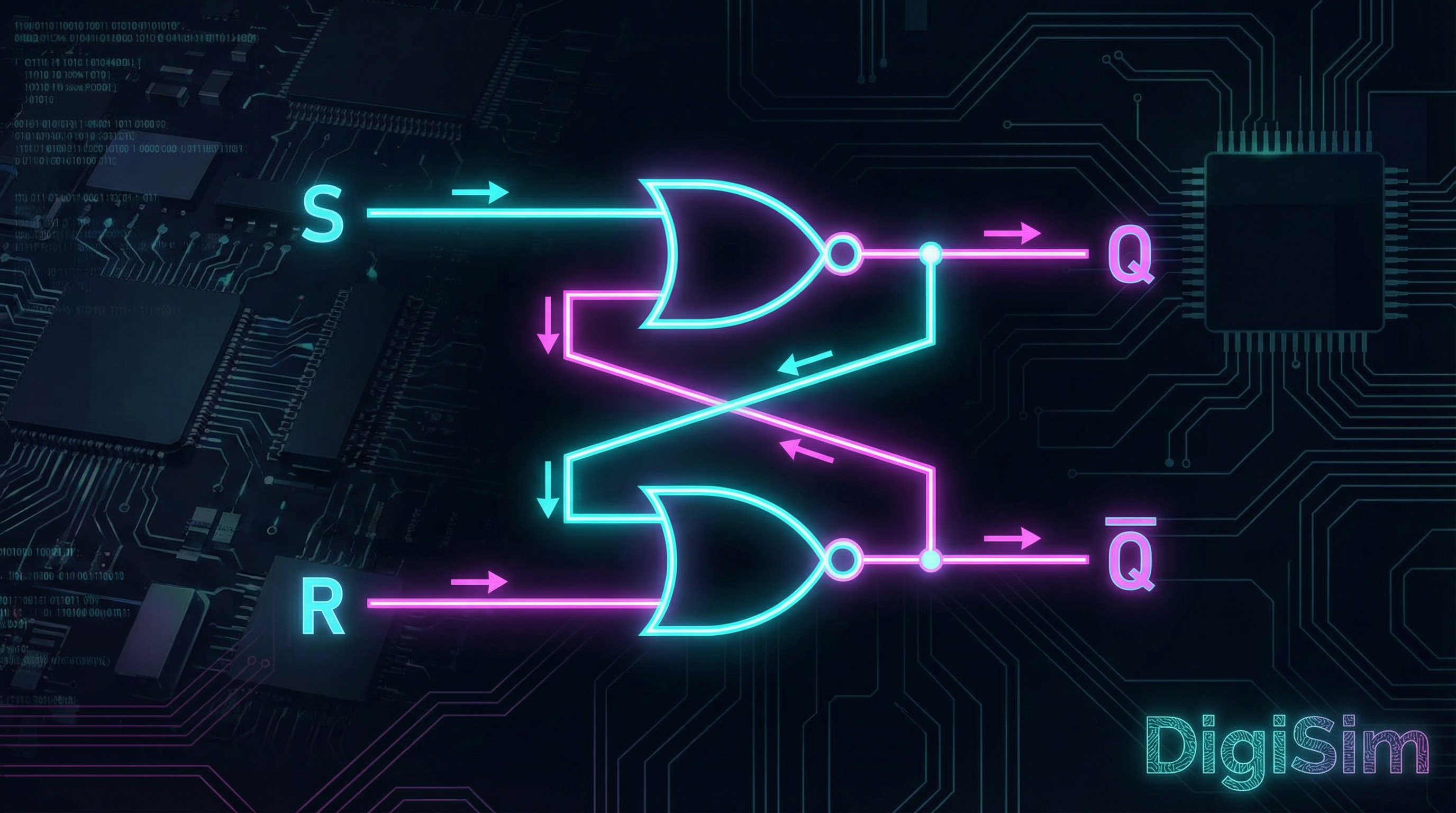

The NOR Gate SR Latch

Imagine two NOR gates. The output of the first gate is wired to one of the inputs of the second gate. The output of the second gate is then wired back to one of the inputs of the first. This feedback loop is the magic that enables memory. The remaining free inputs on each gate become our S and R lines.

Visually, the connections are:

- The top NOR gate has inputs R and the output of the bottom NOR gate (). Its output is Q.

- The bottom NOR gate has inputs S and the output of the top NOR gate (Q). Its output is .

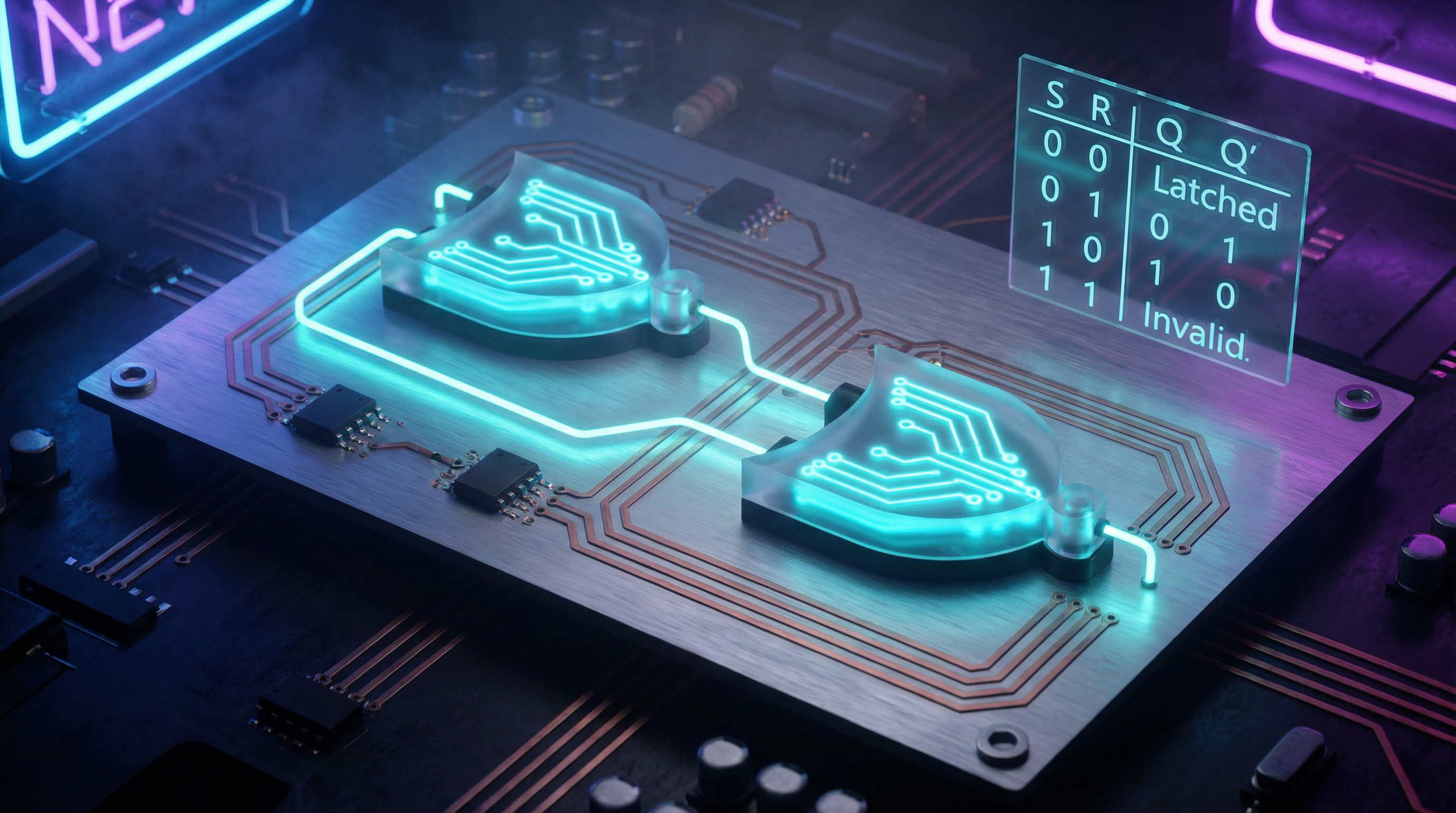

Let’s analyze its behavior through its truth table.

| S | R | Q | Action | |

|---|---|---|---|---|

| 0 | 0 | Q | Hold (Memory) | |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 0 | 1 | 0 | Set |

| 1 | 1 | 0 | 0 | Invalid |

Let’s trace the logic:

- Reset (S=0, R=1): The ‘1’ on the R input forces the output of the top NOR gate (Q) to ‘0’. This ‘0’ is fed to the bottom NOR gate along with S=0. With both inputs at ‘0’, the bottom NOR gate’s output () becomes ‘1’. The circuit is stable at Q=0.

- Set (S=1, R=0): The ‘1’ on the S input forces the output of the bottom NOR gate () to ‘0’. This ‘0’ is fed to the top NOR gate along with R=0. With both inputs at ‘0’, the top NOR gate’s output (Q) becomes ‘1’. The circuit is stable at Q=1.

- Hold (S=0, R=0): If the latch was just Set (Q=1, =0), the ‘1’ from Q feeds back to the bottom gate, keeping at ‘0’. This ‘0’ from feeds back to the top gate, keeping Q at ‘1’. The state holds itself. The same self-reinforcing logic applies if the latch was previously Reset.

Boolean Logic: The Math Behind the Memory

We can express the behavior of the NOR-based SR Latch with a characteristic equation. The output Q is determined by the R input and the output of the other gate, .

However, we know that is itself a function of S and Q:

Substituting the second equation into the first gives us the complete picture of the feedback loop. When S=0 and R=0 (the hold state), the equation for Q simplifies to , which reduces to , or simply . This mathematically confirms that the next state is equal to the current state—the definition of memory.

The NAND Gate SR Latch

The SR Latch can also be built from two cross-coupled NAND gates. The key difference is that the NAND implementation is active-low, meaning the inputs assert their function when driven to logic ‘0’ rather than ‘1’. For clarity, the inputs are often written as and .

| Q | Action | |||

|---|---|---|---|---|

| 1 | 1 | Q | Hold (Memory) | |

| 1 | 0 | 1 | 0 | Set |

| 0 | 1 | 0 | 1 | Reset |

| 0 | 0 | 1 | 1 | Invalid |

Notice the symmetry with the NOR version: the truth table is effectively inverted. The hold state now requires both inputs to be ‘1’ (inactive), and the forbidden state occurs when both inputs are ‘0’ (both active). The NAND-based latch is common in practice because many integrated circuit families natively provide NAND gates, and active-low control signals are widespread in digital systems.

Common Pitfall: The Forbidden State

Look closely at the last row of each truth table: S=1, R=1 for the NOR version, and =0, =0 for the NAND version. We call this the “forbidden” or “invalid” state. Why?

- Logical Contradiction: In the NOR implementation, when S=1, the bottom NOR gate’s output () is forced to 0. When R=1, the top NOR gate’s output (Q) is also forced to 0. This means , which violates the fundamental principle that an output and its complement must be opposites. In the NAND version, the same simultaneous assertion forces both Q and to 1—an equally invalid condition.

- Race Condition: The real danger occurs when the inputs transition from the forbidden state back to the hold state. Both gates will try to re-evaluate their outputs simultaneously. Which one “wins”? The result depends on minuscule differences in manufacturing, wire length, and temperature—a classic race condition. The final state of the latch becomes unpredictable, which is unacceptable in a reliable digital system.

- Metastability Risk: In a physical circuit, the race condition can push the internal nodes to an intermediate voltage—neither a clean ‘0’ nor a clean ‘1’. This metastable state may persist for an indeterminate amount of time before randomly resolving to one state or the other, potentially causing downstream logic failures.

This is why in any practical design, you must ensure the S and R inputs are never active at the same time. This limitation is precisely what led to the development of more advanced memory circuits like D-Latches and JK Flip-Flops.

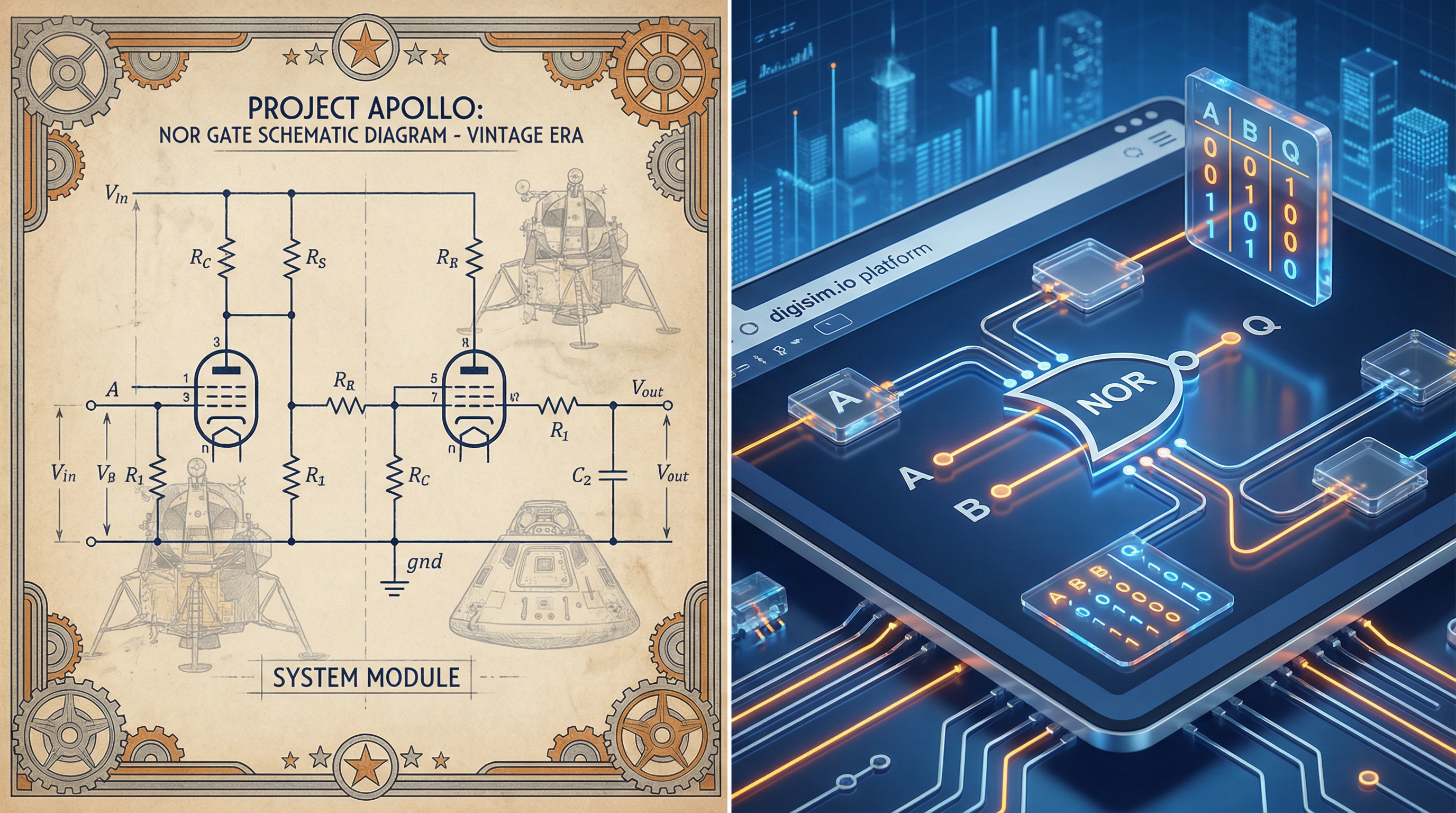

Simulating on digisim.io

Theory is one thing, but seeing a circuit in action provides true understanding. Let’s build and test an SR Latch on the digisim.io platform.

- Open the Simulator: Navigate to the digisim.io workspace.

- Place Components: From the component library, drag two NOR gates, two Input switches (for S and R), and two Output LEDs (for Q and ).

- Wire the Latch:

- Connect the first Input switch to one input of the bottom NOR gate. Label this switch ‘S’.

- Connect the second Input switch to one input of the top NOR gate. Label this switch ‘R’.

- Connect the output of the top NOR gate to the input of its corresponding LED (label it ‘Q’) AND to the second input of the bottom NOR gate. This is the feedback path.

- Connect the output of the bottom NOR gate to the input of its LED (label it '') AND to the second input of the top NOR gate. This completes the cross-coupling.

- Experiment:

- Start with S=0 and R=0. The initial state may be random.

- Set: Click the S switch to ‘1’. Observe that Q becomes ‘1’ and becomes ‘0’.

- Hold: Click S back to ‘0’. Notice the outputs don’t change. The latch has remembered the Set command.

- Reset: Click the R switch to ‘1’. Observe Q flipping to ‘0’ and to ‘1’.

- Hold Again: Click R back to ‘0’. The outputs remain in the Reset state.

- Test the Forbidden State: Set both S and R to ‘1’. You will see both Q and go to ‘0’. Now, try to set both back to ‘0’ at the exact same time. The simulator will likely resolve to a deterministic state, but in a real-world physical circuit, this outcome would be unreliable.

Real-World Use Cases

The SR Latch isn’t just a textbook curiosity. Its principles are at work all around us.

- Mechanical Switch Debouncing: When you press a physical button, the mechanical contacts don’t close cleanly. They “bounce” several times, creating a rapid series of on-off signals. If this noisy signal were fed directly to a counter, it might register dozens of presses instead of one. An SR latch solves this elegantly. The first bounce Sets (or Resets) the latch, and subsequent bounces on the same contact have no effect. The latch produces a single, clean output pulse.

- Foundation for Complex Memory: While you won’t find a simple SR Latch acting as your computer’s main memory, it is the conceptual ancestor of the static RAM (SRAM) cells used in CPU caches and registers. More advanced, clock-synchronized versions (like D Flip-Flops) are built directly upon the latch’s bistable foundation. A 64-bit CPU register is, at its heart, a collection of 64 sophisticated memory elements that evolved from this simple cross-coupled design.

The SR Latch is a masterclass in digital simplicity. With just two gates—whether NOR or NAND—it introduces the concept of state: the ability to hold information over time. While its forbidden state requires careful management, its role as the fundamental building block of memory makes it one of the most important circuits you will ever learn. Every D latch, every flip-flop, every register in every CPU traces its lineage back to this cross-coupled pair of gates.

Ready to see this in action? Head over to digisim.io and build your own SR Latch. Try both the NOR and NAND implementations, experiment with their states, witness the feedback loop, and prove to yourself how two simple gates can create the foundation of memory.